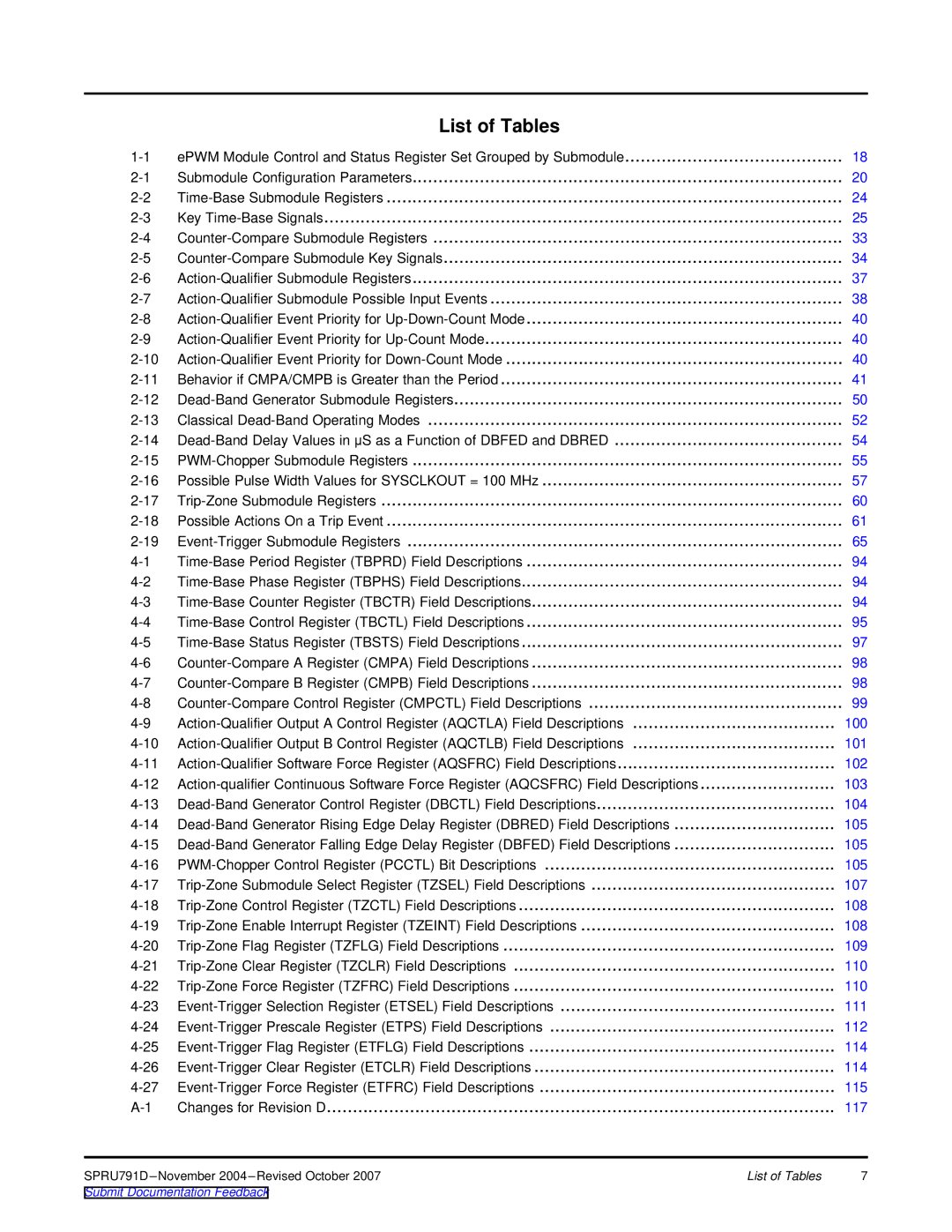

List of Tables

ePWM Module Control and Status Register Set Grouped by Submodule | 18 | ||

Submodule Configuration Parameters | 20 | ||

24 | |||

Key | 25 | ||

33 | |||

34 | |||

37 | |||

38 | |||

40 | |||

40 | |||

40 | |||

Behavior if CMPA/CMPB is Greater than the Period | 41 | ||

50 | |||

Classical | 52 | ||

54 | |||

55 | |||

Possible Pulse Width Values for SYSCLKOUT = 100 MHz | 57 | ||

60 | |||

Possible Actions On a Trip Event | 61 | ||

65 | |||

94 | |||

94 | |||

94 | |||

95 | |||

97 | |||

98 | |||

98 | |||

99 | |||

100 | |||

101 | |||

102 | |||

103 | |||

104 | |||

105 | |||

105 | |||

105 | |||

107 | |||

108 | |||

108 | |||

109 | |||

110 | |||

| 110 | ||

111 | |||

112 | |||

114 | |||

114 | |||

115 | |||

Changes for Revision D | 117 | ||

List of Tables | 7 | ||