www.ti.com

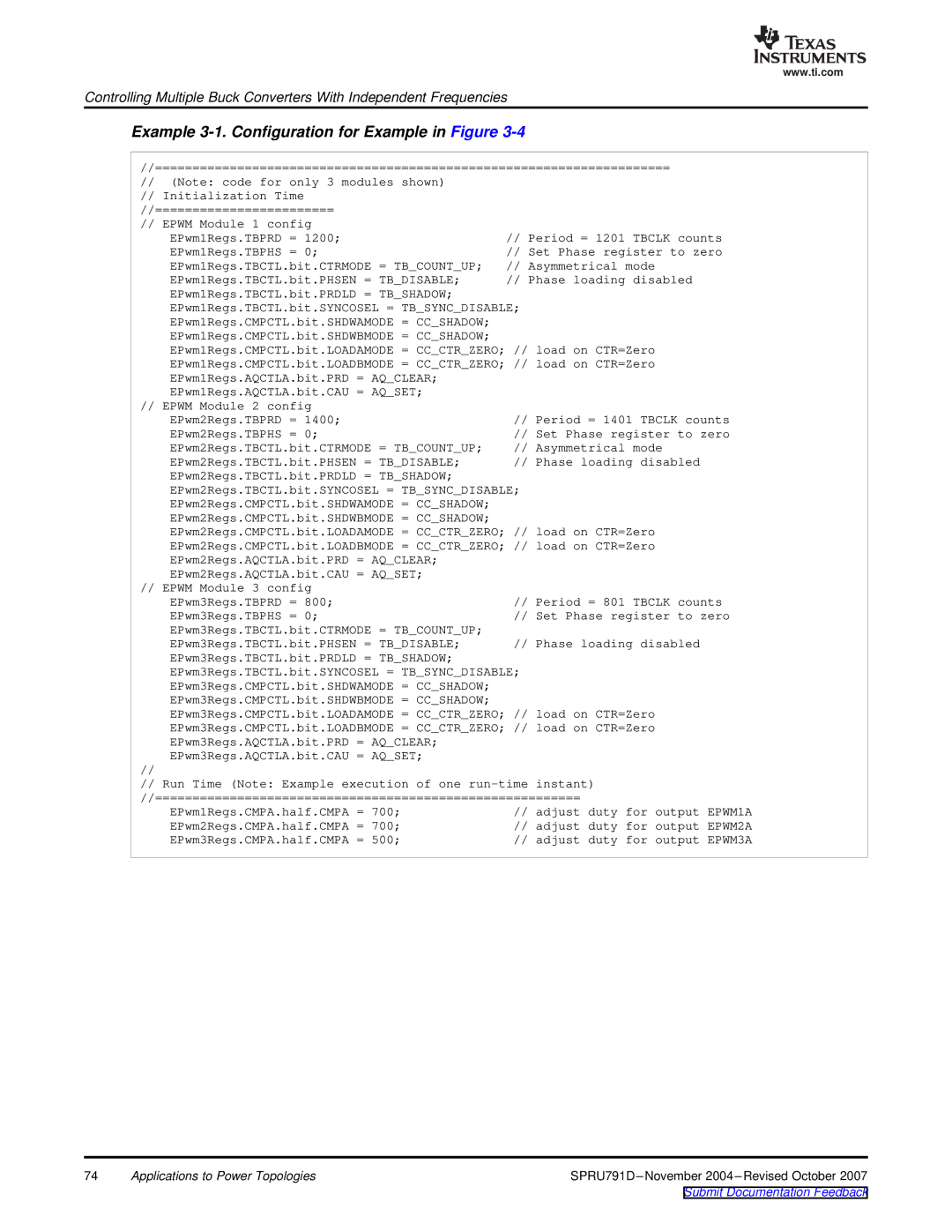

Controlling Multiple Buck Converters With Independent Frequencies

Example 3-1. Configuration for Example in Figure 3-4

//=====================================================================

// (Note: code for only 3 modules shown) |

|

// Initialization Time |

|

//======================== |

|

// EPWM Module 1 config |

|

EPwm1Regs.TBPRD = 1200; | // Period = 1201 TBCLK counts |

EPwm1Regs.TBPHS = 0; | // Set Phase register to zero |

EPwm1Regs.TBCTL.bit.CTRMODE = TB_COUNT_UP; | // Asymmetrical mode |

EPwm1Regs.TBCTL.bit.PHSEN = TB_DISABLE; | // Phase loading disabled |

EPwm1Regs.TBCTL.bit.PRDLD = TB_SHADOW; |

|

EPwm1Regs.TBCTL.bit.SYNCOSEL = TB_SYNC_DISABLE; | |

EPwm1Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW; |

|

EPwm1Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW; |

|

EPwm1Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO; // load on CTR=Zero | |

EPwm1Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO; // load on CTR=Zero | |

EPwm1Regs.AQCTLA.bit.PRD = AQ_CLEAR; |

|

EPwm1Regs.AQCTLA.bit.CAU = AQ_SET; |

|

// EPWM Module 2 config |

|

EPwm2Regs.TBPRD = 1400; | // Period = 1401 TBCLK counts |

EPwm2Regs.TBPHS = 0; | // Set Phase register to zero |

EPwm2Regs.TBCTL.bit.CTRMODE = TB_COUNT_UP; | // Asymmetrical mode |

EPwm2Regs.TBCTL.bit.PHSEN = TB_DISABLE; | // Phase loading disabled |

EPwm2Regs.TBCTL.bit.PRDLD = TB_SHADOW; |

|

EPwm2Regs.TBCTL.bit.SYNCOSEL = TB_SYNC_DISABLE; | |

EPwm2Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW; |

|

EPwm2Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW; |

|

EPwm2Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO; // load on CTR=Zero | |

EPwm2Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO; // load on CTR=Zero | |

EPwm2Regs.AQCTLA.bit.PRD = AQ_CLEAR; |

|

EPwm2Regs.AQCTLA.bit.CAU = AQ_SET; |

|

// EPWM Module 3 config |

|

EPwm3Regs.TBPRD = 800; | // Period = 801 TBCLK counts |

EPwm3Regs.TBPHS = 0; | // Set Phase register to zero |

EPwm3Regs.TBCTL.bit.CTRMODE = TB_COUNT_UP; |

|

EPwm3Regs.TBCTL.bit.PHSEN = TB_DISABLE; | // Phase loading disabled |

EPwm3Regs.TBCTL.bit.PRDLD = TB_SHADOW; |

|

EPwm3Regs.TBCTL.bit.SYNCOSEL = TB_SYNC_DISABLE; EPwm3Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW; EPwm3Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW; EPwm3Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO; // load on CTR=Zero EPwm3Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO; // load on CTR=Zero EPwm3Regs.AQCTLA.bit.PRD = AQ_CLEAR; EPwm3Regs.AQCTLA.bit.CAU = AQ_SET;

//

//Run Time (Note: Example execution of one

EPwm1Regs.CMPA.half.CMPA = 700; | // adjust duty for output EPWM1A | |||

EPwm2Regs.CMPA.half.CMPA | = | 700; | // adjust duty for | output EPWM2A |

EPwm3Regs.CMPA.half.CMPA | = | 500; | // adjust duty for | output EPWM3A |

74 | Applications to Power Topologies |