www.ti.com

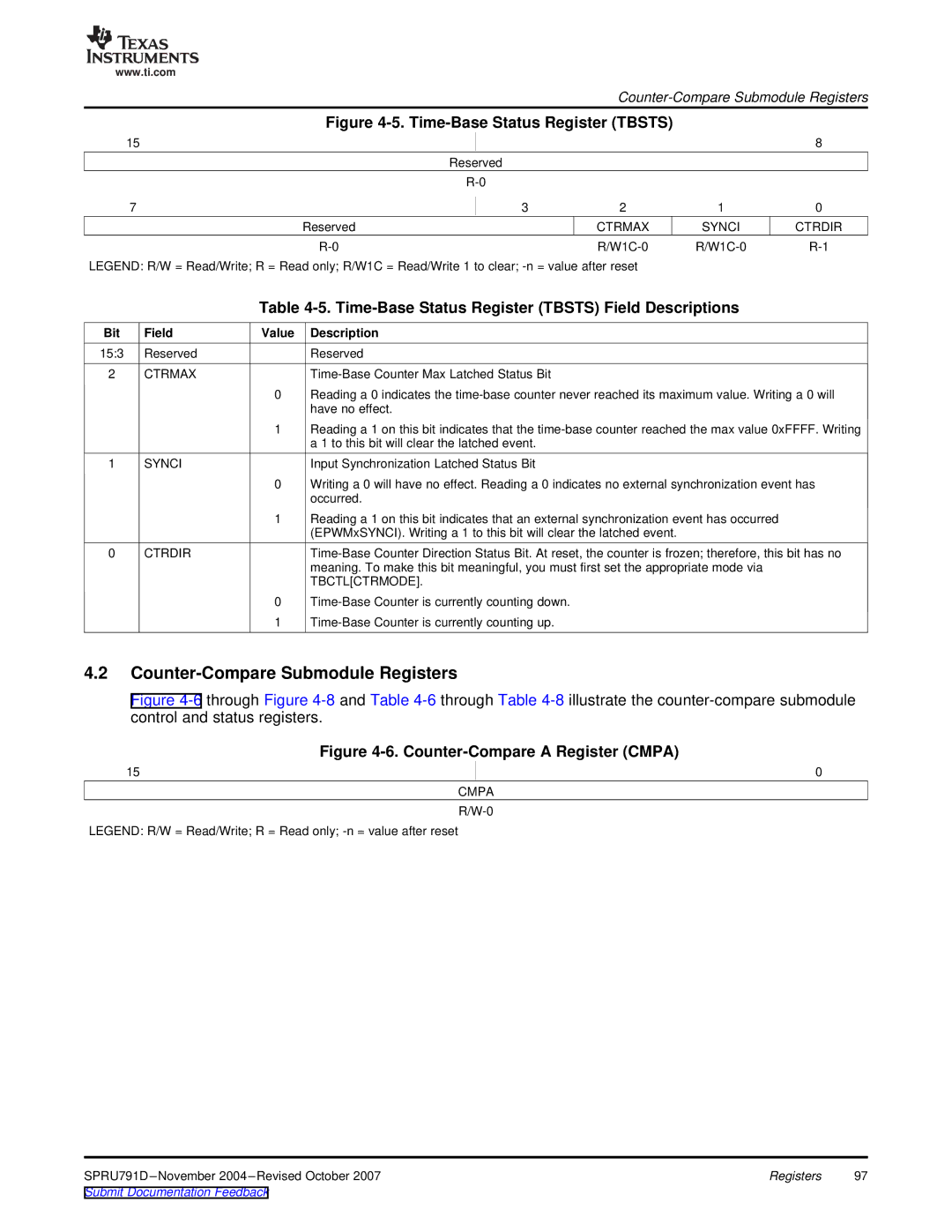

Figure 4-5. Time-Base Status Register (TBSTS)

15 |

|

|

| 8 |

| Reserved |

|

|

|

|

|

|

| |

7 | 3 | 2 | 1 | 0 |

Reserved |

| CTRMAX | SYNCI | CTRDIR |

| ||||

LEGEND: R/W = Read/Write; R = Read only; R/W1C = Read/Write 1 to clear; |

|

| ||

Table 4-5. Time-Base Status Register (TBSTS) Field Descriptions

Bit | Field | Value | Description |

15:3 | Reserved |

| Reserved |

2 | CTRMAX |

| |

|

| 0 | Reading a 0 indicates the |

|

|

| have no effect. |

|

| 1 | Reading a 1 on this bit indicates that the |

|

|

| a 1 to this bit will clear the latched event. |

1 | SYNCI |

| Input Synchronization Latched Status Bit |

|

| 0 | Writing a 0 will have no effect. Reading a 0 indicates no external synchronization event has |

|

|

| occurred. |

|

| 1 | Reading a 1 on this bit indicates that an external synchronization event has occurred |

|

|

| (EPWMxSYNCI). Writing a 1 to this bit will clear the latched event. |

0 | CTRDIR |

| |

|

|

| meaning. To make this bit meaningful, you must first set the appropriate mode via |

|

|

| TBCTL[CTRMODE]. |

|

| 0 | |

|

| 1 |

4.2Counter-Compare Submodule Registers

Figure 4-6 through Figure 4-8 and Table 4-6 through Table 4-8 illustrate the counter-compare submodule control and status registers.

Figure 4-6. Counter-Compare A Register (CMPA)

15 | 0 |

CMPA

LEGEND: R/W = Read/Write; R = Read only;

Registers | 97 | |

Submit Documentation Feedback |

|

|