www.ti.com

|

| Table | |

Bits | Name | Description | |

CMPA | The value in the active CMPA register is continuously compared to the | ||

|

| the values are equal, the | |

|

| compare A" event. This event is sent to the | |

|

| or more actions. These actions can be applied to either the EPWMxA or the EPWMxB output depending | |

|

| on the configuration of the AQCTLA and AQCTLB registers. The actions that can be defined in the | |

|

| AQCTLA and AQCTLB registers include: | |

|

| ∙ | Do nothing; the event is ignored. |

|

| ∙ | Clear: Pull the EPWMxA and/or EPWMxB signal low |

|

| ∙ | Set: Pull the EPWMxA and/or EPWMxB signal high |

|

| ∙ | Toggle the EPWMxA and/or EPWMxB signal |

Shadowing of this register is enabled and disabled by the CMPCTL[SHDWAMODE] bit. By default this register is shadowed.

∙If CMPCTL[SHDWAMODE] = 0, then the shadow is enabled and any write or read will automatically go to the shadow register. In this case, the CMPCTL[LOADAMODE] bit field determines which event will load the active register from the shadow register.

∙Before a write, the CMPCTL[SHDWAFULL] bit can be read to determine if the shadow register is currently full.

∙If CMPCTL[SHDWAMODE] = 1, then the shadow register is disabled and any write or read will go directly to the active register, that is the register actively controlling the hardware.

∙In either mode, the active and shadow registers share the same memory map address.

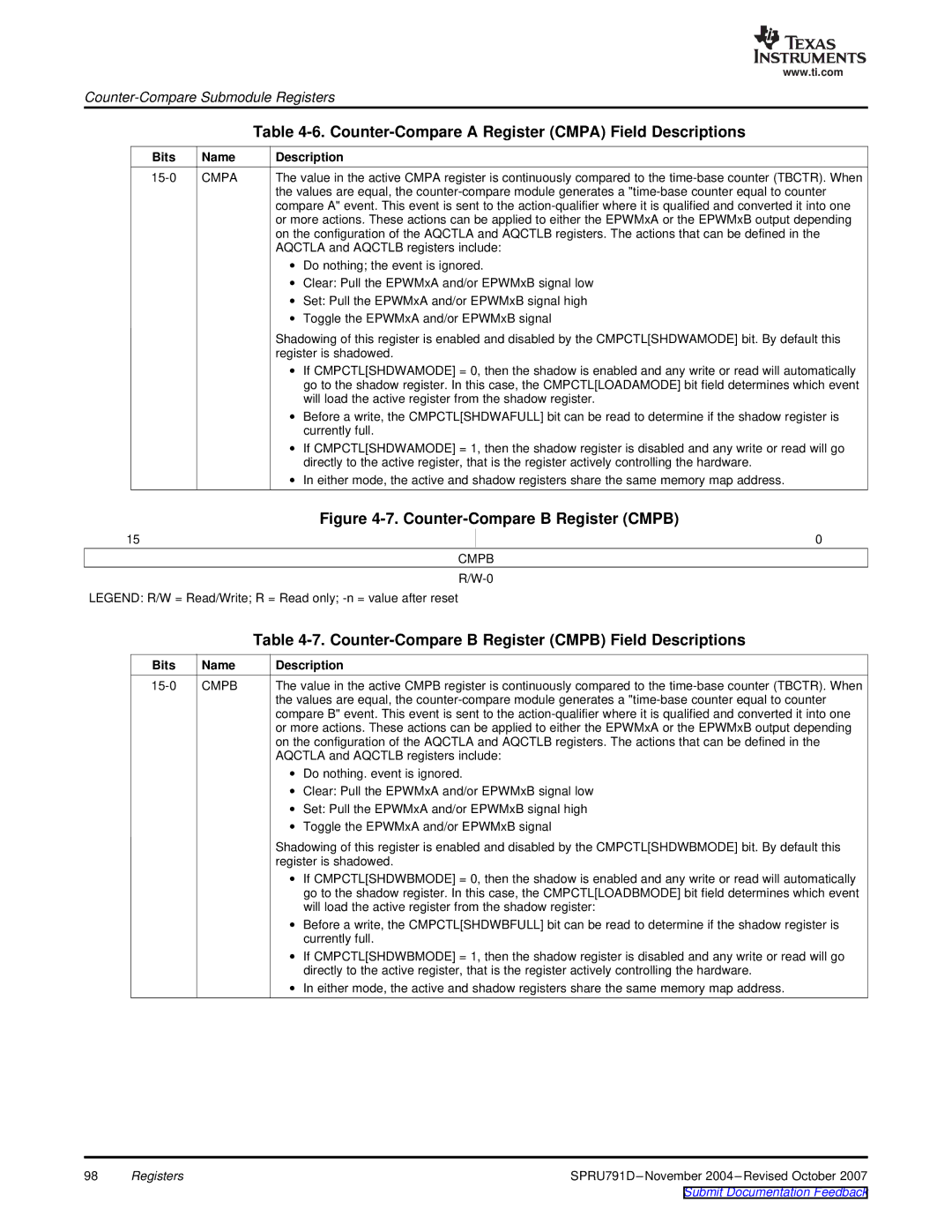

Figure 4-7. Counter-Compare B Register (CMPB)

15 | 0 |

CMPB

LEGEND: R/W = Read/Write; R = Read only;

|

| Table | |

Bits | Name | Description | |

CMPB | The value in the active CMPB register is continuously compared to the | ||

|

| the values are equal, the | |

|

| compare B" event. This event is sent to the | |

|

| or more actions. These actions can be applied to either the EPWMxA or the EPWMxB output depending | |

|

| on the configuration of the AQCTLA and AQCTLB registers. The actions that can be defined in the | |

|

| AQCTLA and AQCTLB registers include: | |

|

| ∙ | Do nothing. event is ignored. |

|

| ∙ | Clear: Pull the EPWMxA and/or EPWMxB signal low |

|

| ∙ | Set: Pull the EPWMxA and/or EPWMxB signal high |

|

| ∙ | Toggle the EPWMxA and/or EPWMxB signal |

Shadowing of this register is enabled and disabled by the CMPCTL[SHDWBMODE] bit. By default this register is shadowed.

∙If CMPCTL[SHDWBMODE] = 0, then the shadow is enabled and any write or read will automatically go to the shadow register. In this case, the CMPCTL[LOADBMODE] bit field determines which event will load the active register from the shadow register:

∙Before a write, the CMPCTL[SHDWBFULL] bit can be read to determine if the shadow register is currently full.

∙If CMPCTL[SHDWBMODE] = 1, then the shadow register is disabled and any write or read will go directly to the active register, that is the register actively controlling the hardware.

∙In either mode, the active and shadow registers share the same memory map address.

98 | Registers |