www.ti.com

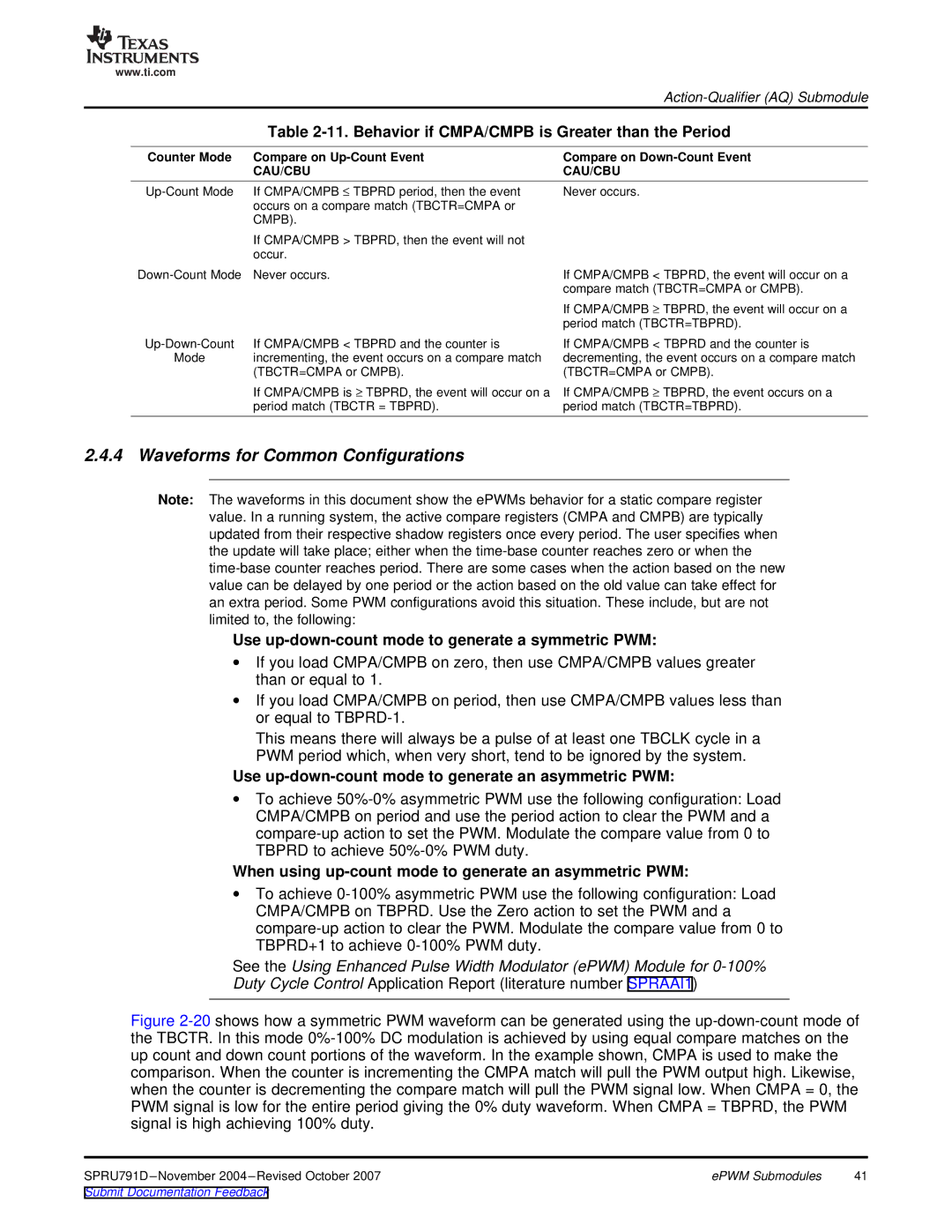

Table 2-11. Behavior if CMPA/CMPB is Greater than the Period

Counter Mode | Compare on |

| CAU/CBU |

If CMPA/CMPB ≤ TBPRD period, then the event | |

| occurs on a compare match (TBCTR=CMPA or |

| CMPB). |

| If CMPA/CMPB > TBPRD, then the event will not |

| occur. |

Never occurs. | |

If CMPA/CMPB < TBPRD and the counter is | |

Mode | incrementing, the event occurs on a compare match |

| (TBCTR=CMPA or CMPB). |

| If CMPA/CMPB is ≥ TBPRD, the event will occur on a |

| period match (TBCTR = TBPRD). |

Compare on

CAU/CBU

Never occurs.

If CMPA/CMPB < TBPRD, the event will occur on a compare match (TBCTR=CMPA or CMPB).

If CMPA/CMPB ≥ TBPRD, the event will occur on a period match (TBCTR=TBPRD).

If CMPA/CMPB < TBPRD and the counter is decrementing, the event occurs on a compare match (TBCTR=CMPA or CMPB).

If CMPA/CMPB ≥ TBPRD, the event occurs on a period match (TBCTR=TBPRD).

2.4.4 Waveforms for Common Configurations

Note: The waveforms in this document show the ePWMs behavior for a static compare register value. In a running system, the active compare registers (CMPA and CMPB) are typically updated from their respective shadow registers once every period. The user specifies when the update will take place; either when the

Use up-down-count mode to generate a symmetric PWM:

∙If you load CMPA/CMPB on zero, then use CMPA/CMPB values greater than or equal to 1.

∙If you load CMPA/CMPB on period, then use CMPA/CMPB values less than or equal to

This means there will always be a pulse of at least one TBCLK cycle in a

PWM period which, when very short, tend to be ignored by the system.

Use up-down-count mode to generate an asymmetric PWM:

∙To achieve

When using up-count mode to generate an asymmetric PWM:

∙To achieve

See the Using Enhanced Pulse Width Modulator (ePWM) Module for

Duty Cycle Control Application Report (literature number SPRAAI1)

Figure 2-20 shows how a symmetric PWM waveform can be generated using the up-down-count mode of the TBCTR. In this mode 0%-100% DC modulation is achieved by using equal compare matches on the up count and down count portions of the waveform. In the example shown, CMPA is used to make the comparison. When the counter is incrementing the CMPA match will pull the PWM output high. Likewise, when the counter is decrementing the compare match will pull the PWM signal low. When CMPA = 0, the PWM signal is low for the entire period giving the 0% duty waveform. When CMPA = TBPRD, the PWM signal is high achieving 100% duty.

ePWM Submodules | 41 |