www.ti.com

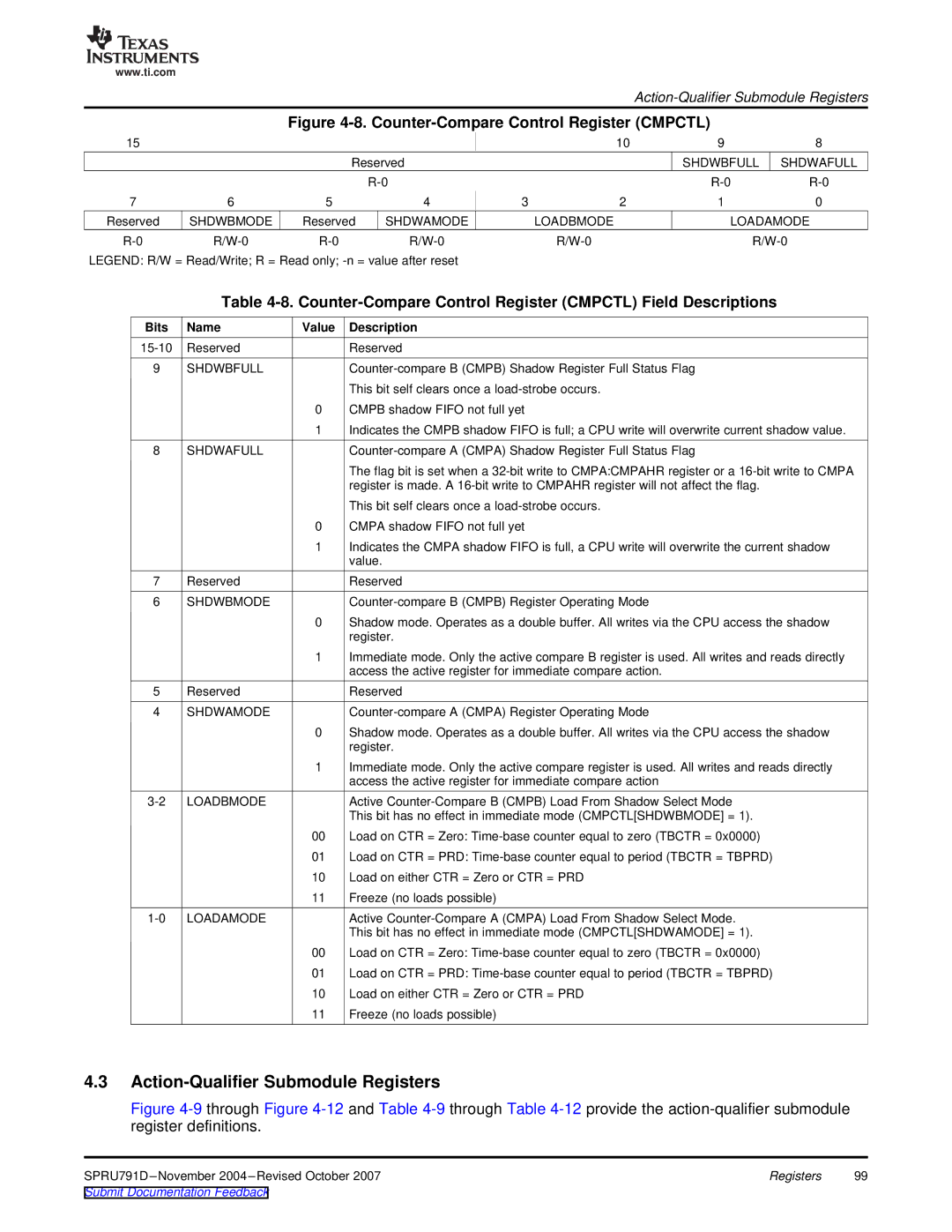

Figure 4-8. Counter-Compare Control Register (CMPCTL)

15 |

|

|

|

| 10 | 9 | 8 |

|

| Reserved |

|

| SHDWBFULL | SHDWAFULL | |

|

|

|

|

| |||

7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

Reserved | SHDWBMODE | Reserved | SHDWAMODE | LOADBMODE |

| LOADAMODE | |

| |||||||

LEGEND: R/W = Read/Write; R = Read only;

Table 4-8. Counter-Compare Control Register (CMPCTL) Field Descriptions

Bits | Name | Value | Description |

Reserved |

| Reserved | |

9 | SHDWBFULL |

| |

|

|

| This bit self clears once a |

|

| 0 | CMPB shadow FIFO not full yet |

|

| 1 | Indicates the CMPB shadow FIFO is full; a CPU write will overwrite current shadow value. |

8 | SHDWAFULL |

| |

|

|

| The flag bit is set when a |

|

|

| register is made. A |

|

|

| This bit self clears once a |

|

| 0 | CMPA shadow FIFO not full yet |

|

| 1 | Indicates the CMPA shadow FIFO is full, a CPU write will overwrite the current shadow |

|

|

| value. |

7 | Reserved |

| Reserved |

6 | SHDWBMODE |

| |

|

| 0 | Shadow mode. Operates as a double buffer. All writes via the CPU access the shadow |

|

|

| register. |

|

| 1 | Immediate mode. Only the active compare B register is used. All writes and reads directly |

|

|

| access the active register for immediate compare action. |

5 | Reserved |

| Reserved |

4 | SHDWAMODE |

| |

|

| 0 | Shadow mode. Operates as a double buffer. All writes via the CPU access the shadow |

|

|

| register. |

|

| 1 | Immediate mode. Only the active compare register is used. All writes and reads directly |

|

|

| access the active register for immediate compare action |

LOADBMODE |

| Active | |

|

|

| This bit has no effect in immediate mode (CMPCTL[SHDWBMODE] = 1). |

|

| 00 | Load on CTR = Zero: |

|

| 01 | Load on CTR = PRD: |

|

| 10 | Load on either CTR = Zero or CTR = PRD |

|

| 11 | Freeze (no loads possible) |

LOADAMODE |

| Active | |

|

|

| This bit has no effect in immediate mode (CMPCTL[SHDWAMODE] = 1). |

|

| 00 | Load on CTR = Zero: |

|

| 01 | Load on CTR = PRD: |

|

| 10 | Load on either CTR = Zero or CTR = PRD |

|

| 11 | Freeze (no loads possible) |

4.3Action-Qualifier Submodule Registers

Figure 4-9 through Figure 4-12 and Table 4-9 through Table 4-12 provide the action-qualifier submodule register definitions.

Registers | 99 |