www.ti.com

Proper Interrupt Initialization Procedure

4.8Proper Interrupt Initialization Procedure

When the ePWM peripheral clock is enabled it may be possible that interrupt flags may be set due to spurious events due to the ePWM registers not being properly initialized. The proper procedure for initializing the ePWM peripheral is as follows:

1.Disable Global Interrupts (CPU INTM flag)

2.Disable ePWM Interrupts

3.Initialize Peripheral Registers

4.Clear Any Spurious ePWM Flags (including PIEIFR)

5.Enable ePWM Interrupts

6.Enable Global Interrupts

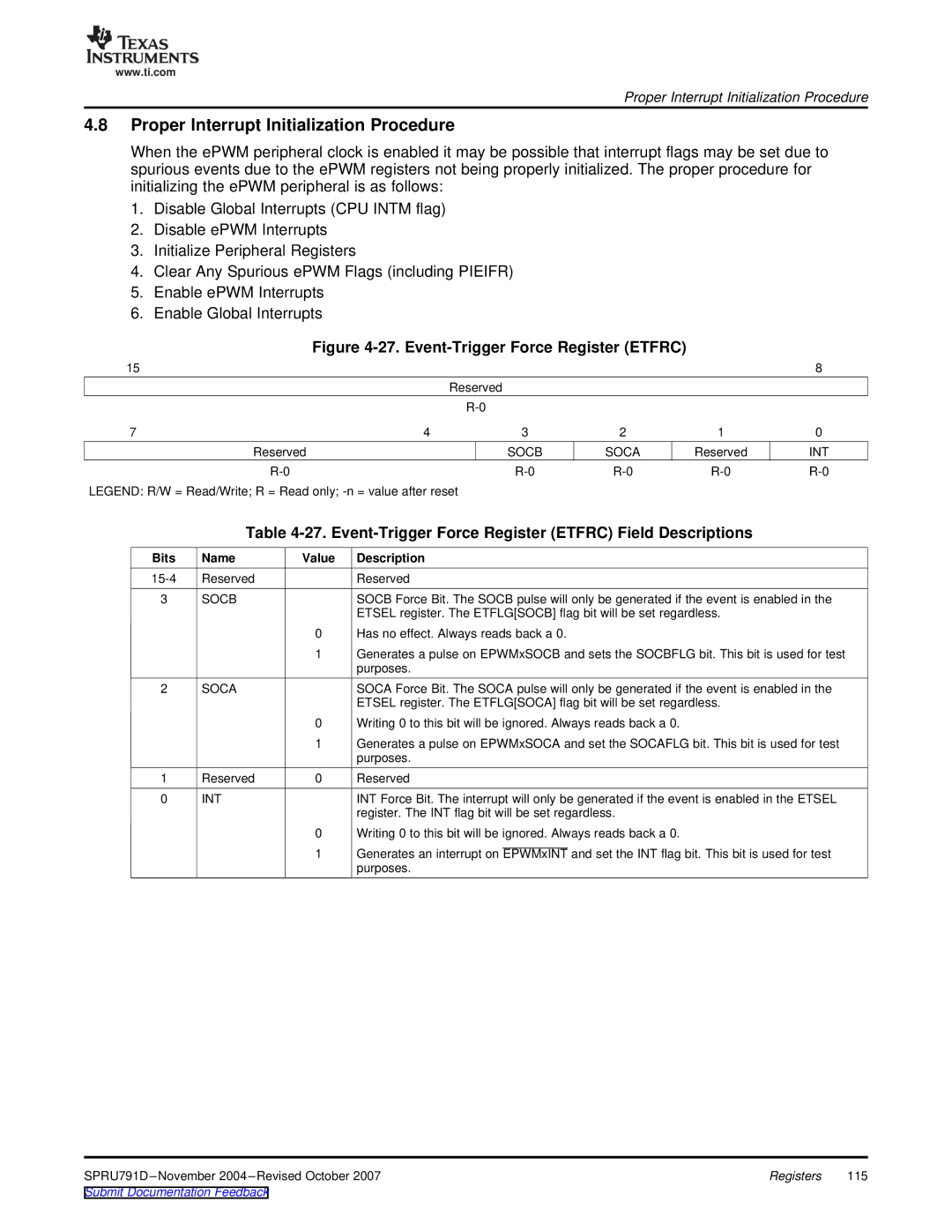

Figure 4-27. Event-Trigger Force Register (ETFRC)

15 |

|

|

|

| 8 |

|

| Reserved |

|

|

|

|

|

|

|

| |

7 | 4 | 3 | 2 | 1 | 0 |

Reserved |

| SOCB | SOCA | Reserved | INT |

|

LEGEND: R/W = Read/Write; R = Read only;

Table 4-27. Event-Trigger Force Register (ETFRC) Field Descriptions

Bits | Name | Value | Description |

Reserved |

| Reserved | |

3 | SOCB |

| SOCB Force Bit. The SOCB pulse will only be generated if the event is enabled in the |

|

|

| ETSEL register. The ETFLG[SOCB] flag bit will be set regardless. |

|

| 0 | Has no effect. Always reads back a 0. |

|

| 1 | Generates a pulse on EPWMxSOCB and sets the SOCBFLG bit. This bit is used for test |

|

|

| purposes. |

2 | SOCA |

| SOCA Force Bit. The SOCA pulse will only be generated if the event is enabled in the |

|

|

| ETSEL register. The ETFLG[SOCA] flag bit will be set regardless. |

|

| 0 | Writing 0 to this bit will be ignored. Always reads back a 0. |

|

| 1 | Generates a pulse on EPWMxSOCA and set the SOCAFLG bit. This bit is used for test |

|

|

| purposes. |

1 | Reserved | 0 | Reserved |

0 | INT |

| INT Force Bit. The interrupt will only be generated if the event is enabled in the ETSEL |

|

|

| register. The INT flag bit will be set regardless. |

|

| 0 | Writing 0 to this bit will be ignored. Always reads back a 0. |

|

| 1 | Generates an interrupt on EPWMxINT and set the INT flag bit. This bit is used for test |

|

|

| purposes. |

Registers | 115 |