www.ti.com

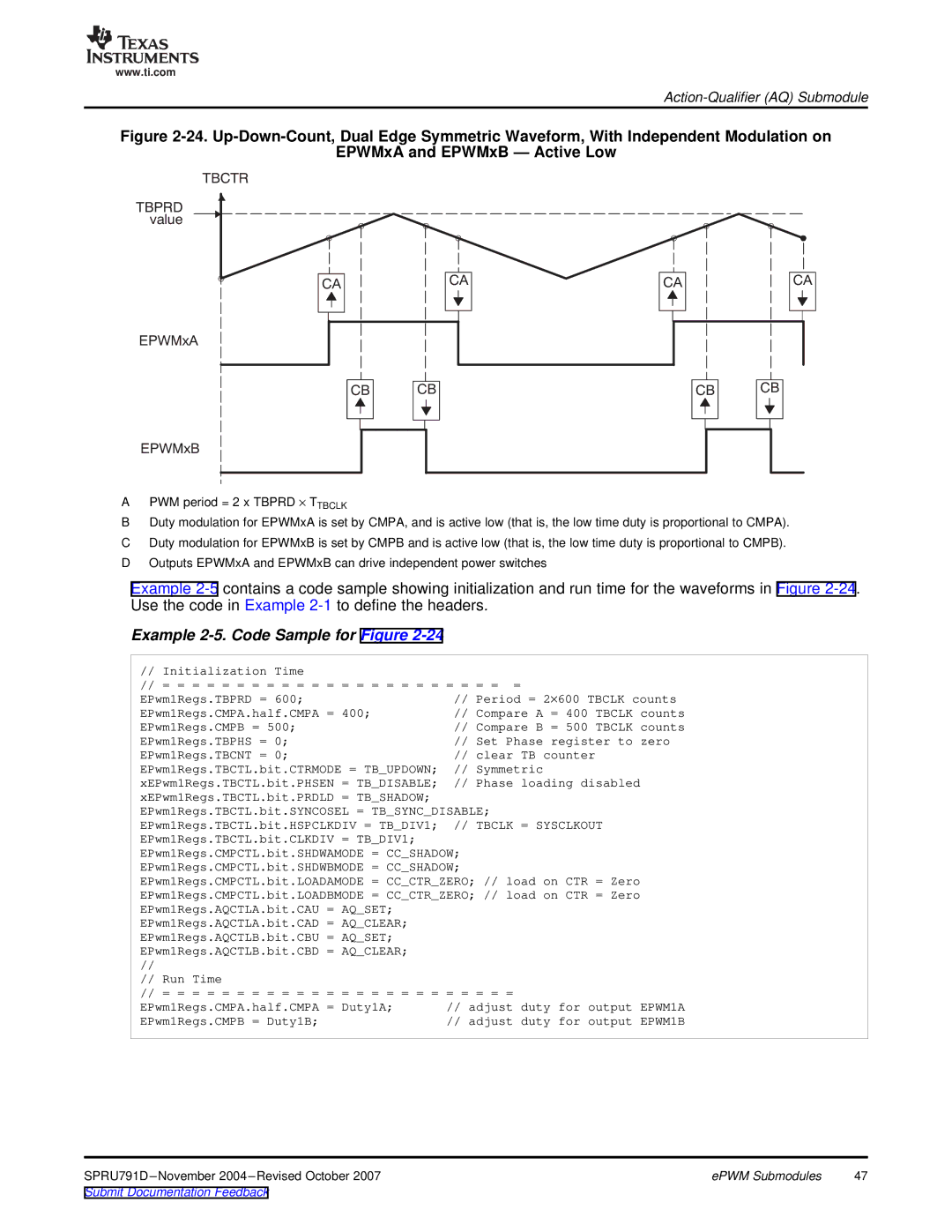

Figure 2-24. Up-Down-Count, Dual Edge Symmetric Waveform, With Independent Modulation on

EPWMxA and EPWMxB — Active Low

TBCTR

TBPRD value

CA

CA

CA

CA

EPWMxA

CB

CB

CB

CB

EPWMxB

APWM period = 2 x TBPRD × TTBCLK

BDuty modulation for EPWMxA is set by CMPA, and is active low (that is, the low time duty is proportional to CMPA).

CDuty modulation for EPWMxB is set by CMPB and is active low (that is, the low time duty is proportional to CMPB).

DOutputs EPWMxA and EPWMxB can drive independent power switches

Example

Example 2-5. Code Sample for Figure 2-24

//Initialization Time

//= = = = = = = = = = = = = = = = = = = = = = = =

EPwm1Regs.TBPRD = 600; | // Period = 2×600 TBCLK counts |

EPwm1Regs.CMPA.half.CMPA = 400; | // Compare A = 400 TBCLK counts |

EPwm1Regs.CMPB = 500; | // Compare B = 500 TBCLK counts |

EPwm1Regs.TBPHS = 0; | // Set Phase register to zero |

EPwm1Regs.TBCNT = 0; | // clear TB counter |

EPwm1Regs.TBCTL.bit.CTRMODE = TB_UPDOWN; | // Symmetric |

xEPwm1Regs.TBCTL.bit.PHSEN = TB_DISABLE; | // Phase loading disabled |

xEPwm1Regs.TBCTL.bit.PRDLD = TB_SHADOW; |

|

EPwm1Regs.TBCTL.bit.SYNCOSEL = TB_SYNC_DISABLE; | |

EPwm1Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1; | // TBCLK = SYSCLKOUT |

EPwm1Regs.TBCTL.bit.CLKDIV = TB_DIV1; |

|

EPwm1Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;

EPwm1Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW; EPwm1Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO; // load on CTR = Zero EPwm1Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO; // load on CTR = Zero EPwm1Regs.AQCTLA.bit.CAU = AQ_SET;

EPwm1Regs.AQCTLA.bit.CAD = AQ_CLEAR;

EPwm1Regs.AQCTLB.bit.CBU = AQ_SET;

EPwm1Regs.AQCTLB.bit.CBD = AQ_CLEAR;

//

//Run Time

//= = = = = = = = = = = = = = = = = = = = = = = =

EPwm1Regs.CMPA.half.CMPA | = Duty1A; | // | adjust | duty | for | output | EPWM1A |

EPwm1Regs.CMPB = Duty1B; |

| // | adjust | duty | for | output | EPWM1B |

ePWM Submodules | 47 |