www.ti.com

Example 2-3. Code Sample for Figure 2-22

//Initialization Time

//= = = = = = = = = = = = = = = = = = = = = = = =

EPwm1Regs.TBPRD = 600; | // | Period = 601 TBCLK counts |

EPwm1Regs.CMPA.half.CMPA = 350; | // | Compare A = 350 TBCLK counts |

EPwm1Regs.CMPB = 200; | // | Compare B = 200 TBCLK counts |

EPwm1Regs.TBPHS = 0; | // | Set Phase register to zero |

EPwm1Regs.TBCTR = 0; | // | clear TB counter |

EPwm1Regs.TBCTL.bit.CTRMODE = TB_UP; |

|

|

EPwm1Regs.TBCTL.bit.PHSEN = TB_DISABLE; | // | Phase loading disabled |

EPwm1Regs.TBCTL.bit.PRDLD = TB_SHADOW; |

|

|

EPwm1Regs.TBCTL.bit.SYNCOSEL = TB_SYNC_DISABLE; | ||

EPwm1Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1; // | TBCLK = SYSCLKOUT | |

EPwm1Regs.TBCTL.bit.CLKDIV = TB_DIV1; |

|

|

EPwm1Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW; |

| |

EPwm1Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW; |

| |

EPwm1Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO; // load on TBCTR = Zero EPwm1Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO; // load on TBCTR = Zero EPwm1Regs.AQCTLA.bit.PRD = AQ_CLEAR;

EPwm1Regs.AQCTLA.bit.CAU = AQ_SET;

EPwm1Regs.AQCTLB.bit.PRD = AQ_CLEAR;

EPwm1Regs.AQCTLB.bit.CBU = AQ_SET;

//

//Run Time

//= = = = = = = = = = = = = = = = = = = = = = = =

EPwm1Regs.CMPA.half.CMPA | = Duty1A; | // | adjust | duty | for | output | EPWM1A |

EPwm1Regs.CMPB = Duty1B; |

| // | adjust | duty | for | output | EPWM1B |

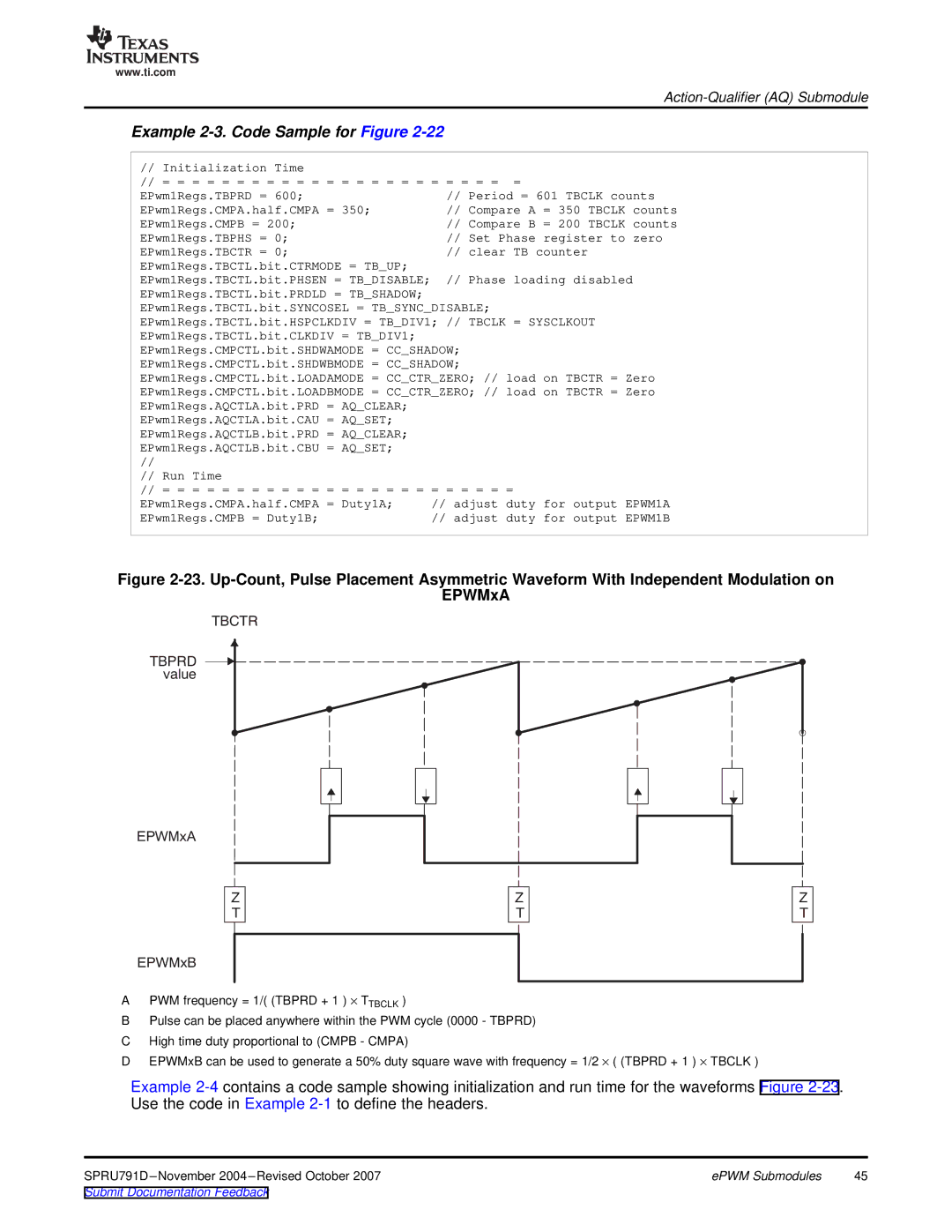

Figure 2-23. Up-Count, Pulse Placement Asymmetric Waveform With Independent Modulation on

EPWMxA

TBCTR

TBPRD value

EPWMxA

Z

T

Z T

Z T

EPWMxB

APWM frequency = 1/( (TBPRD + 1 ) × TTBCLK )

BPulse can be placed anywhere within the PWM cycle (0000 - TBPRD)

CHigh time duty proportional to (CMPB - CMPA)

DEPWMxB can be used to generate a 50% duty square wave with frequency = 1/2 × ( (TBPRD + 1 ) × TBCLK )

Example

ePWM Submodules | 45 |