www.ti.com

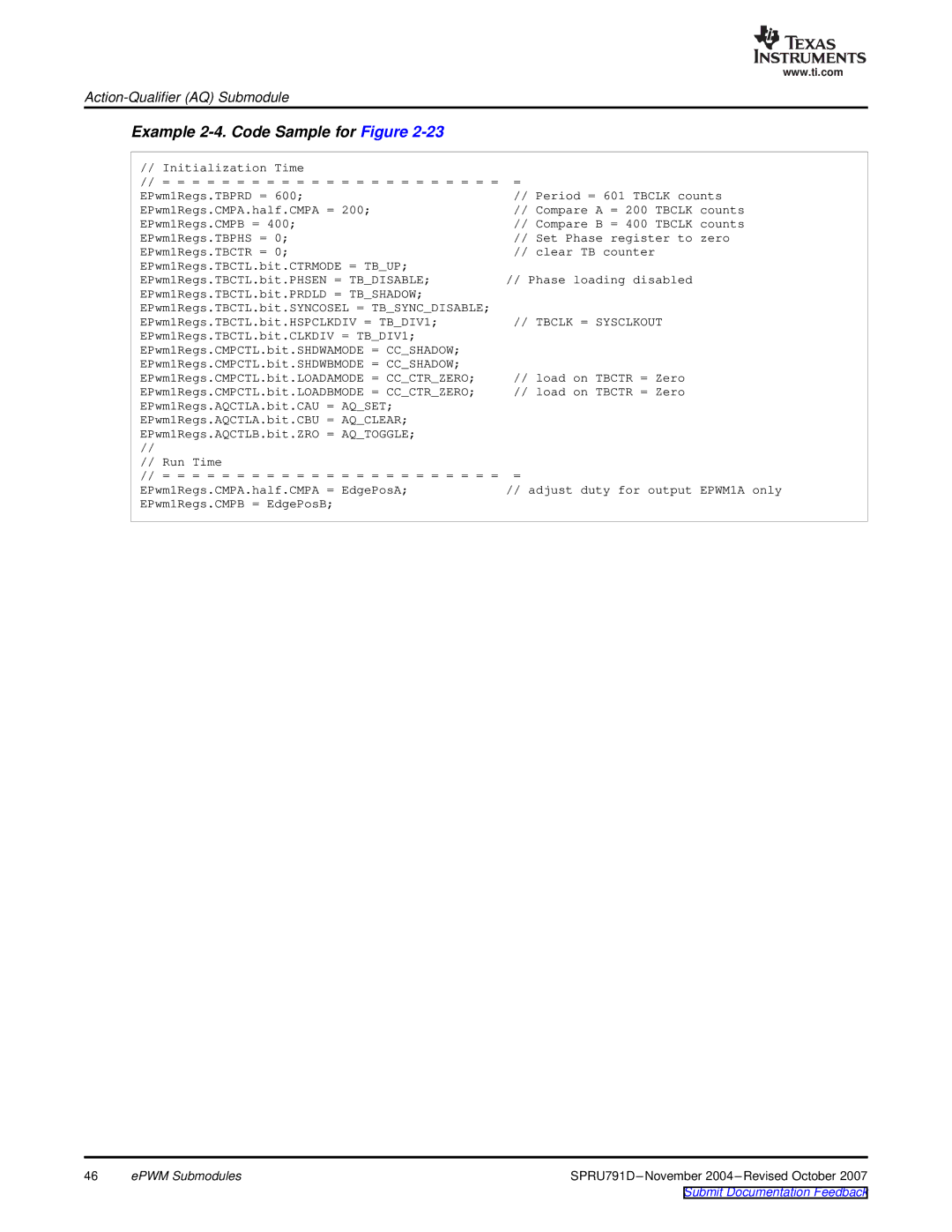

Example 2-4. Code Sample for Figure 2-23

//Initialization Time

//= = = = = = = = = = = = = = = = = = = = = = = =

EPwm1Regs.TBPRD = 600; | // Period = 601 TBCLK counts |

EPwm1Regs.CMPA.half.CMPA = 200; | // Compare A = 200 TBCLK counts |

EPwm1Regs.CMPB = 400; | // Compare B = 400 TBCLK counts |

EPwm1Regs.TBPHS = 0; | // Set Phase register to zero |

EPwm1Regs.TBCTR = 0; | // clear TB counter |

EPwm1Regs.TBCTL.bit.CTRMODE = TB_UP; |

|

EPwm1Regs.TBCTL.bit.PHSEN = TB_DISABLE; | // Phase loading disabled |

EPwm1Regs.TBCTL.bit.PRDLD = TB_SHADOW; |

|

EPwm1Regs.TBCTL.bit.SYNCOSEL = TB_SYNC_DISABLE; |

|

EPwm1Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1; | // TBCLK = SYSCLKOUT |

EPwm1Regs.TBCTL.bit.CLKDIV = TB_DIV1; |

|

EPwm1Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW; |

|

EPwm1Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW; |

|

EPwm1Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO; | // load on TBCTR = Zero |

EPwm1Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO; | // load on TBCTR = Zero |

EPwm1Regs.AQCTLA.bit.CAU = AQ_SET; |

|

EPwm1Regs.AQCTLA.bit.CBU = AQ_CLEAR; |

|

EPwm1Regs.AQCTLB.bit.ZRO = AQ_TOGGLE; |

|

// |

|

//Run Time

//= = = = = = = = = = = = = = = = = = = = = = = =

EPwm1Regs.CMPA.half.CMPA = | EdgePosA; | // adjust duty for output EPWM1A only |

EPwm1Regs.CMPB = EdgePosB; |

|

|

46 | ePWM Submodules |