Troubleshooting

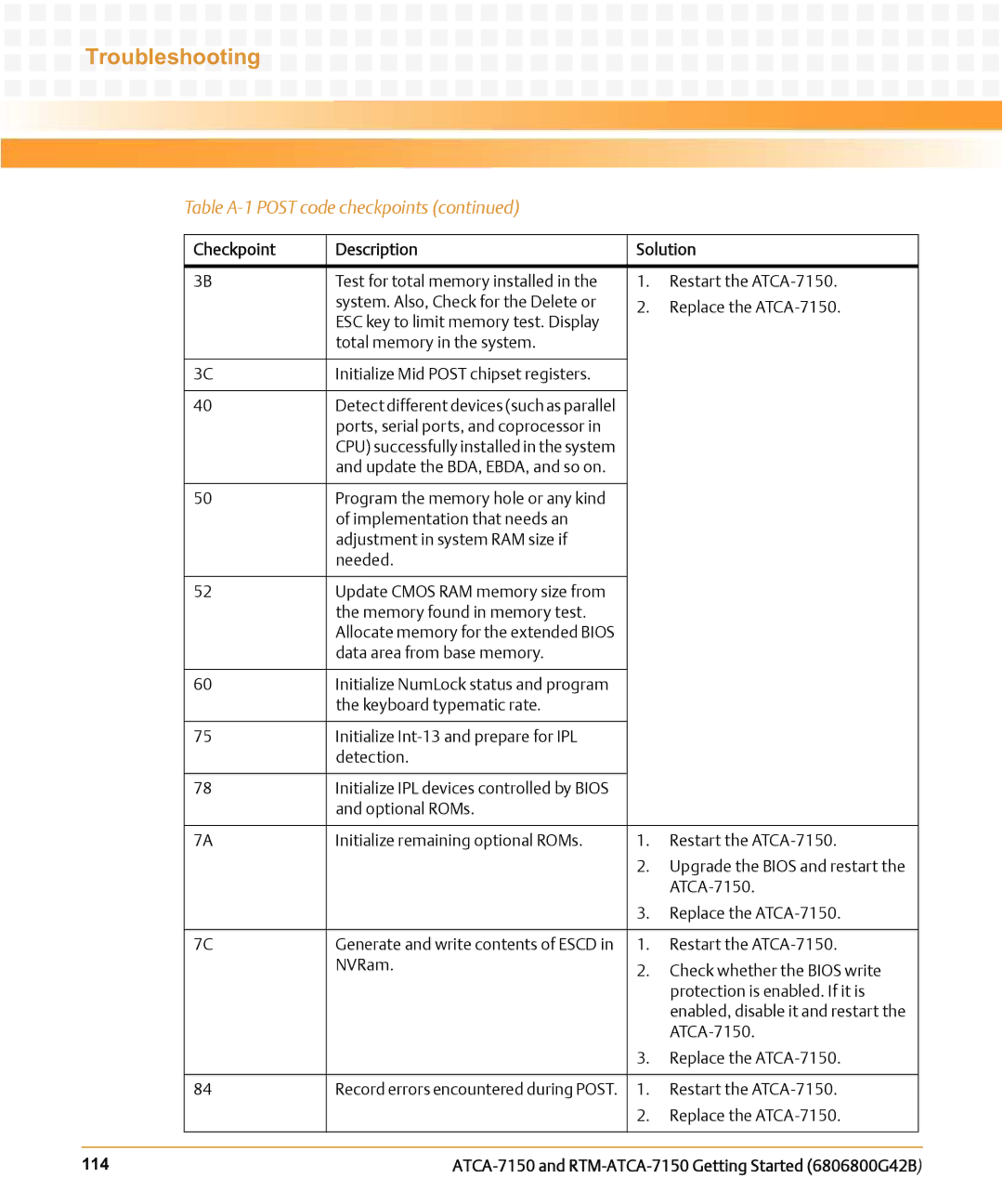

Table A-1 POST code checkpoints (continued)

| Checkpoint | Description | Solution |

| |

|

|

|

|

|

|

| 3B | Test for total memory installed in the | 1. | Restart the |

|

|

| system. Also, Check for the Delete or | 2. | Replace the |

|

|

| ESC key to limit memory test. Display |

| ||

|

|

|

|

| |

|

| total memory in the system. |

|

|

|

|

|

|

|

|

|

| 3C | Initialize Mid POST chipset registers. |

|

|

|

|

|

|

|

|

|

| 40 | Detect different devices (such as parallel |

|

|

|

|

| ports, serial ports, and coprocessor in |

|

|

|

|

| CPU) successfully installed in the system |

|

|

|

|

| and update the BDA, EBDA, and so on. |

|

|

|

|

|

|

|

|

|

| 50 | Program the memory hole or any kind |

|

|

|

|

| of implementation that needs an |

|

|

|

|

| adjustment in system RAM size if |

|

|

|

|

| needed. |

|

|

|

|

|

|

|

|

|

| 52 | Update CMOS RAM memory size from |

|

|

|

|

| the memory found in memory test. |

|

|

|

|

| Allocate memory for the extended BIOS |

|

|

|

|

| data area from base memory. |

|

|

|

|

|

|

|

|

|

| 60 | Initialize NumLock status and program |

|

|

|

|

| the keyboard typematic rate. |

|

|

|

|

|

|

|

|

|

| 75 | Initialize |

|

|

|

|

| detection. |

|

|

|

|

|

|

|

|

|

| 78 | Initialize IPL devices controlled by BIOS |

|

|

|

|

| and optional ROMs. |

|

|

|

|

|

|

|

|

|

| 7A | Initialize remaining optional ROMs. | 1. | Restart the |

|

|

|

| 2. | Upgrade the BIOS and restart the |

|

|

|

|

|

| |

|

|

| 3. | Replace the |

|

|

|

|

|

|

|

| 7C | Generate and write contents of ESCD in | 1. | Restart the |

|

|

| NVRam. | 2. | Check whether the BIOS write |

|

|

|

|

| ||

|

|

|

| protection is enabled. If it is |

|

|

|

|

| enabled, disable it and restart the |

|

|

|

|

|

| |

|

|

| 3. | Replace the |

|

|

|

|

|

|

|

| 84 | Record errors encountered during POST. | 1. | Restart the |

|

|

|

| 2. | Replace the |

|

|

|

|

|

| |

|

|

|

|

|

|

114 |

| ||||