10/100

Datasheet

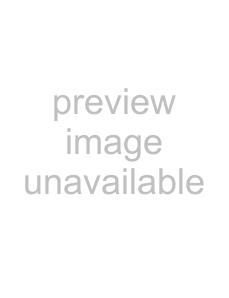

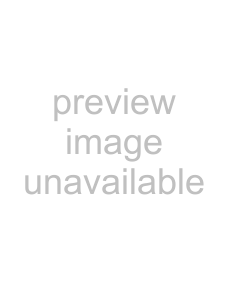

t17 | t12 | t14 |

Clock

t12A

t12A

nDATACS

t17A

t17A

W/nR nCYCLE

| t19 |

| t19 |

Read Data | a | b | c |

t15

t15

nRDYRTN

Figure 14.6 Burst Read Cycles - nVLBUS=1

| PARAMETER | MIN | TYP | MAX | UNITS |

|

|

|

|

|

|

t12 | nDATACS Setup to LCLK Rising | 20 |

|

| ns |

|

|

|

|

|

|

t12A | nDATACS Hold after LCLK Rising | 0 |

|

| ns |

|

|

|

|

|

|

t14 | nRDYRTN Setup to LCLK Falling | 10 |

|

| ns |

|

|

|

|

|

|

t15 | nRDYRTN Hold after LCLK Falling | 10 |

|

| ns |

|

|

|

|

|

|

t17 | W/nR Setup to LCLK Falling | 15 |

|

| ns |

|

|

|

|

|

|

t17A | W/nR Hold After LCLK Falling | 3 |

|

| ns |

|

|

|

|

|

|

t19 | Data Delay from LCLK Rising (Read) | 5 |

| 15 | ns |

|

|

|

|

|

|

Revision 1.91 | 114 | SMSC LAN91C111 REV C |

DATASHEET