10/100

Datasheet

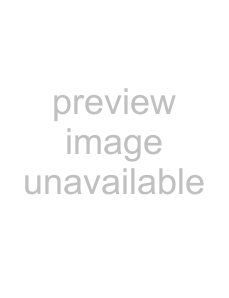

a. Short Bit

3.1V

Slope 0.5 V/ns

Slope 0.5 V/ns

585mV

585 mV sin ( | *t/PW) |

0 | P W |

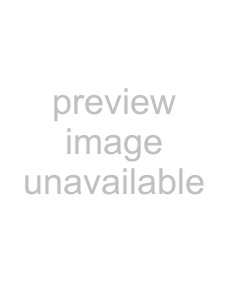

b. Long Bit

3.1V

Slope 0.5 V/ns

585mV

| 585 mV sin (2 * t/PW) |

|

|

| 585 mV sin [2 | (t - PW/2)/PW] |

|

0 | PW/4 | 3PW/4 | PW |

The squelch block determines if the TP input contains valid data. The 100 Mbps TP squelch is one of the criteria used to determine link integrity. The squelch comparators compare the TP inputs against fixed positive and negative thresholds, called squelch levels. The output from the squelch comparator goes to a digital squelch circuit which determines if the receive input data on that channel is valid. If the data is invalid, the receiver is in the squelched state. If the input voltage exceeds the squelch levels at least 4 times with alternating polarity within a 10 μS interval, the data is considered to be valid by the squelch circuit and the receiver now enters into the unsquelch state. In the unsquelch state, the receive threshold level is reduced by approximately 30% for noise immunity reasons and is called the unsquelch level. When the receiver is in the unsquelch state, then the input signal is deemed to be valid. The device stays in the unsquelch state until loss of data is detected. Loss of data is detected if no alternating polarity unsquelch transitions are detected during any 10 μS interval. When the loss of data is detected, the receive squelch is turned on again.

TP Squelch, 10 MbpsThe TP squelch algorithm for 10 Mbps mode is identical to the 100 Mbps mode except, (1) the 10 Mbps TP squelch algorithm is not used for link integrity but to sense the beginning of a packet, (2) the receiver goes into the unsquelch state if the input voltage exceeds the squelch levels for three bit times with alternating polarity within a

Revision 1.91 | 34 | SMSC LAN91C111 REV C |

DATASHEET