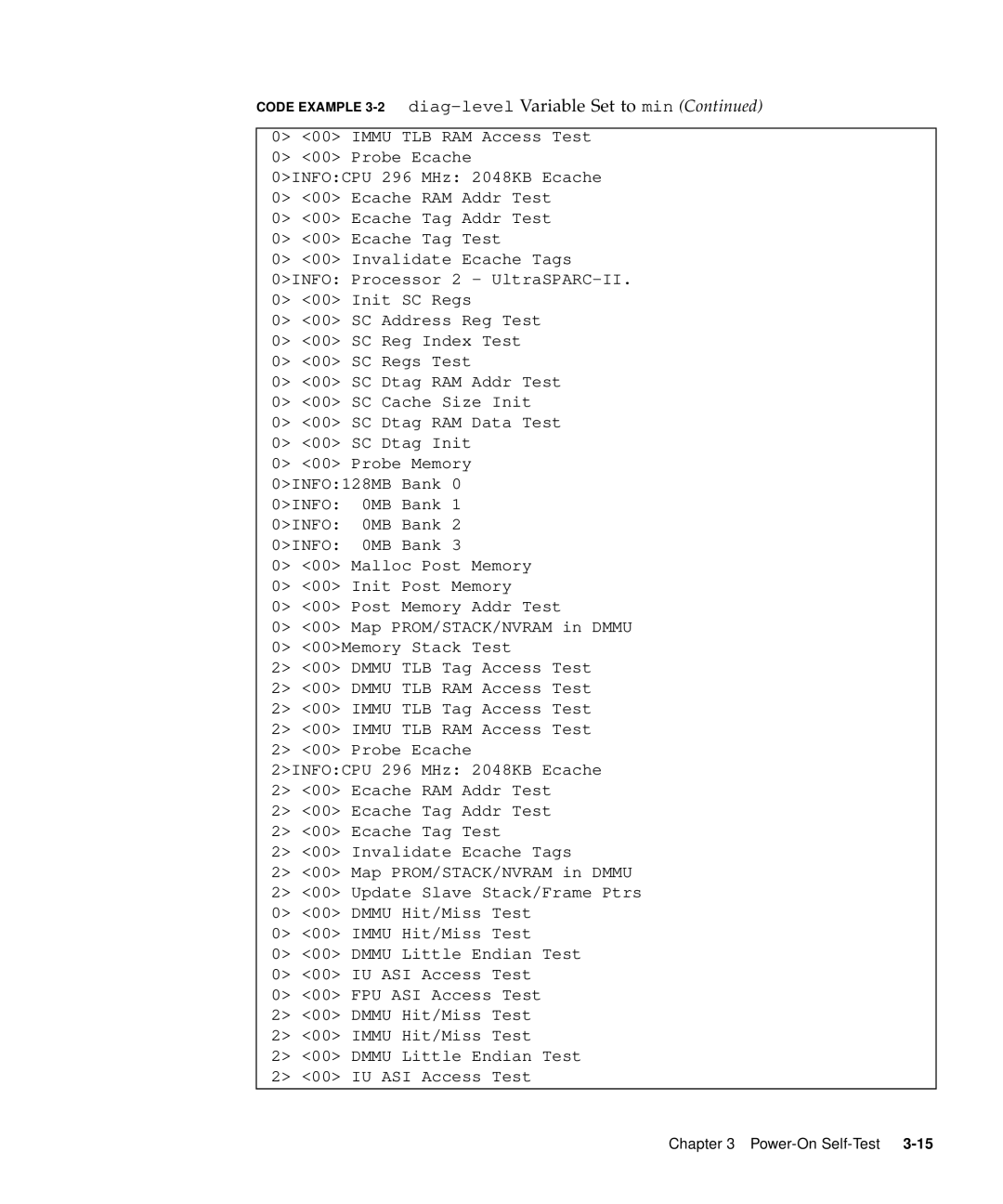

CODE EXAMPLE

0> <00> IMMU TLB RAM Access Test 0> <00> Probe Ecache 0>INFO:CPU 296 MHz: 2048KB Ecache 0> <00> Ecache RAM Addr Test

0> <00> Ecache Tag Addr Test 0> <00> Ecache Tag Test

0> <00> Invalidate Ecache Tags 0>INFO: Processor 2 -

0> <00> SC Address Reg Test

0> <00> SC Reg Index Test 0> <00> SC Regs Test

0> <00> SC Dtag RAM Addr Test 0> <00> SC Cache Size Init 0> <00> SC Dtag RAM Data Test 0> <00> SC Dtag Init

0> <00> Probe Memory 0>INFO:128MB Bank 0 0>INFO: 0MB Bank 1 0>INFO: 0MB Bank 2 0>INFO: 0MB Bank 3

0> <00> Malloc Post Memory

0> <00> Init Post Memory

0> <00> Post Memory Addr Test

0> <00> Map PROM/STACK/NVRAM in DMMU 0> <00>Memory Stack Test

2> <00> DMMU TLB Tag Access Test 2> <00> DMMU TLB RAM Access Test 2> <00> IMMU TLB Tag Access Test 2> <00> IMMU TLB RAM Access Test 2> <00> Probe Ecache 2>INFO:CPU 296 MHz: 2048KB Ecache 2> <00> Ecache RAM Addr Test

2> <00> Ecache Tag Addr Test 2> <00> Ecache Tag Test

2> <00> Invalidate Ecache Tags

2> <00> Map PROM/STACK/NVRAM in DMMU 2> <00> Update Slave Stack/Frame Ptrs 0> <00> DMMU Hit/Miss Test

0> <00> IMMU Hit/Miss Test

0> <00> DMMU Little Endian Test 0> <00> IU ASI Access Test

0> <00> FPU ASI Access Test

2> <00> DMMU Hit/Miss Test

2> <00> IMMU Hit/Miss Test

2> <00> DMMU Little Endian Test 2> <00> IU ASI Access Test