Sundance Technology

ST201

PRELIMINARY draft 2

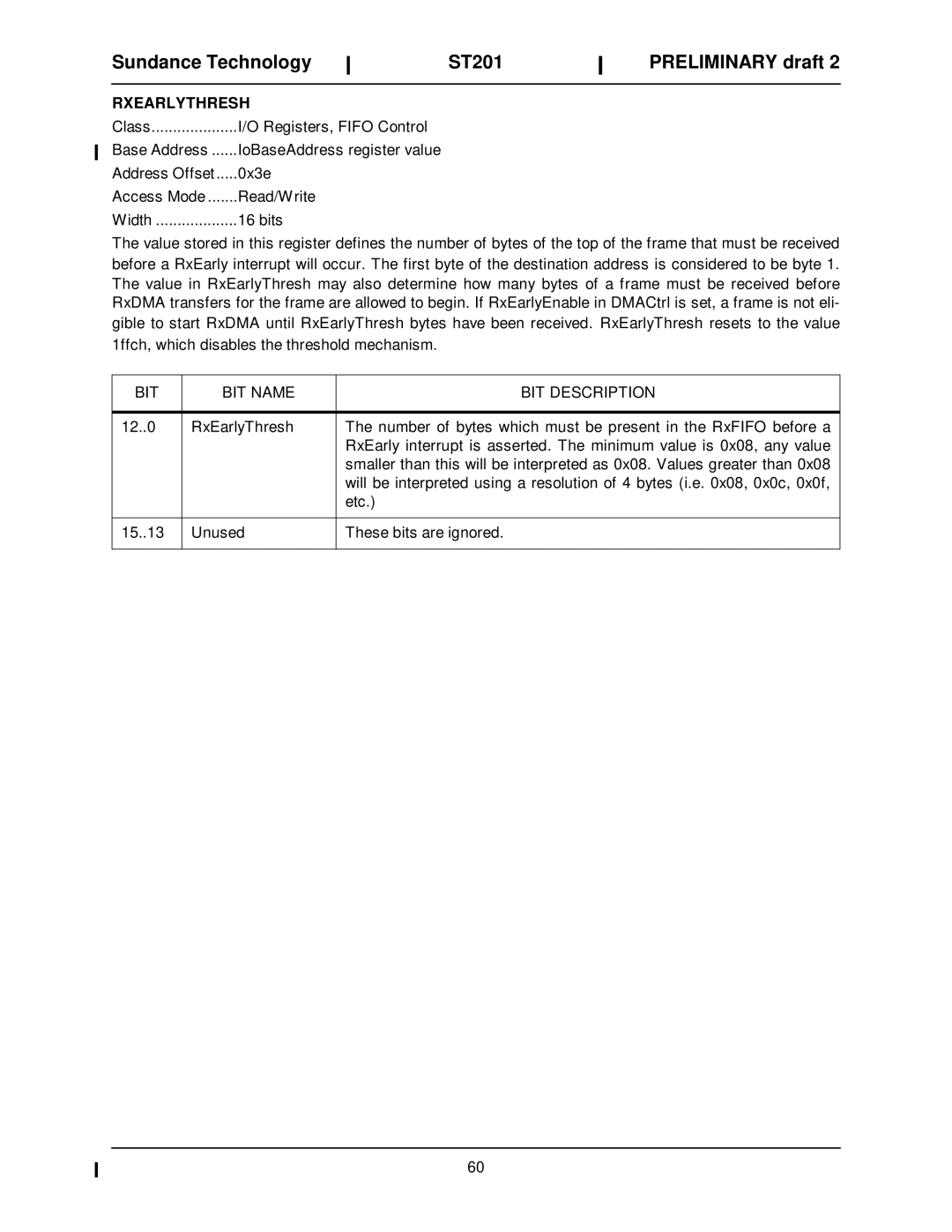

RXEARLYTHRESH

Class | I/O Registers, FIFO Control |

Base Address | IoBaseAddress register value |

Address Offset | 0x3e |

Access Mode | Read/Write |

Width | 16 bits |

The value stored in this register defines the number of bytes of the top of the frame that must be received before a RxEarly interrupt will occur. The first byte of the destination address is considered to be byte 1. The value in RxEarlyThresh may also determine how many bytes of a frame must be received before RxDMA transfers for the frame are allowed to begin. If RxEarlyEnable in DMACtrl is set, a frame is not eli- gible to start RxDMA until RxEarlyThresh bytes have been received. RxEarlyThresh resets to the value 1ffch, which disables the threshold mechanism.

BIT

12..0

15..13

BIT NAME

RxEarlyThresh

Unused

BIT DESCRIPTION

The number of bytes which must be present in the RxFIFO before a RxEarly interrupt is asserted. The minimum value is 0x08, any value smaller than this will be interpreted as 0x08. Values greater than 0x08 will be interpreted using a resolution of 4 bytes (i.e. 0x08, 0x0c, 0x0f, etc.)

These bits are ignored.

60