Sundance Technology

ST201

PRELIMINARY draft 2

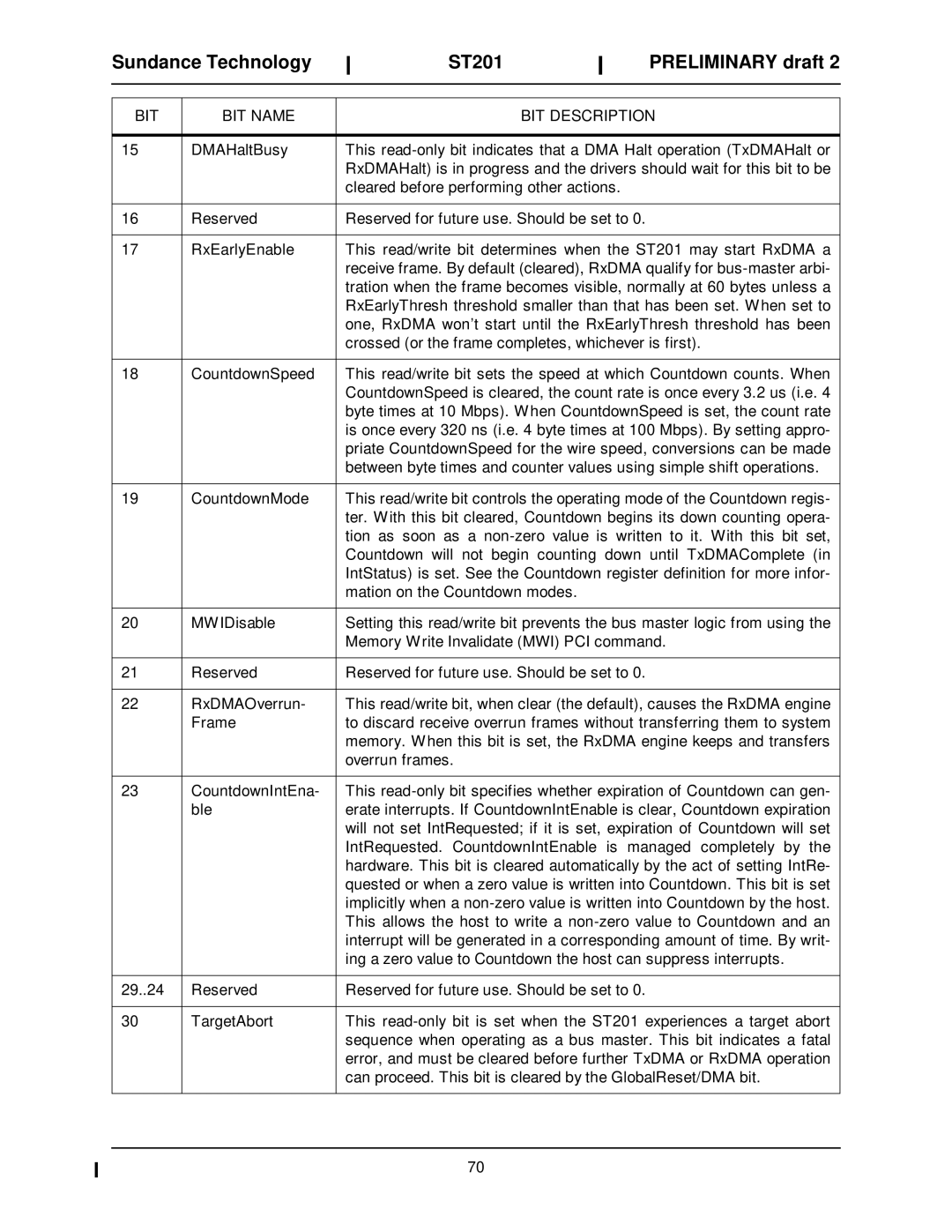

BIT 15

16

17

18

19

20

21

22

23

29..24 30

BIT NAME

DMAHaltBusy

Reserved

RxEarlyEnable

CountdownSpeed

CountdownMode

MWIDisable

Reserved

RxDMAOverrun- Frame

CountdownIntEna- ble

Reserved

TargetAbort

BIT DESCRIPTION

This

Reserved for future use. Should be set to 0.

This read/write bit determines when the ST201 may start RxDMA a receive frame. By default (cleared), RxDMA qualify for

This read/write bit sets the speed at which Countdown counts. When CountdownSpeed is cleared, the count rate is once every 3.2 us (i.e. 4 byte times at 10 Mbps). When CountdownSpeed is set, the count rate is once every 320 ns (i.e. 4 byte times at 100 Mbps). By setting appro- priate CountdownSpeed for the wire speed, conversions can be made between byte times and counter values using simple shift operations.

This read/write bit controls the operating mode of the Countdown regis- ter. With this bit cleared, Countdown begins its down counting opera- tion as soon as a

Setting this read/write bit prevents the bus master logic from using the Memory Write Invalidate (MWI) PCI command.

Reserved for future use. Should be set to 0.

This read/write bit, when clear (the default), causes the RxDMA engine to discard receive overrun frames without transferring them to system memory. When this bit is set, the RxDMA engine keeps and transfers overrun frames.

This

Reserved for future use. Should be set to 0.

This

70