Sundance Technology

BIT | BIT NAME |

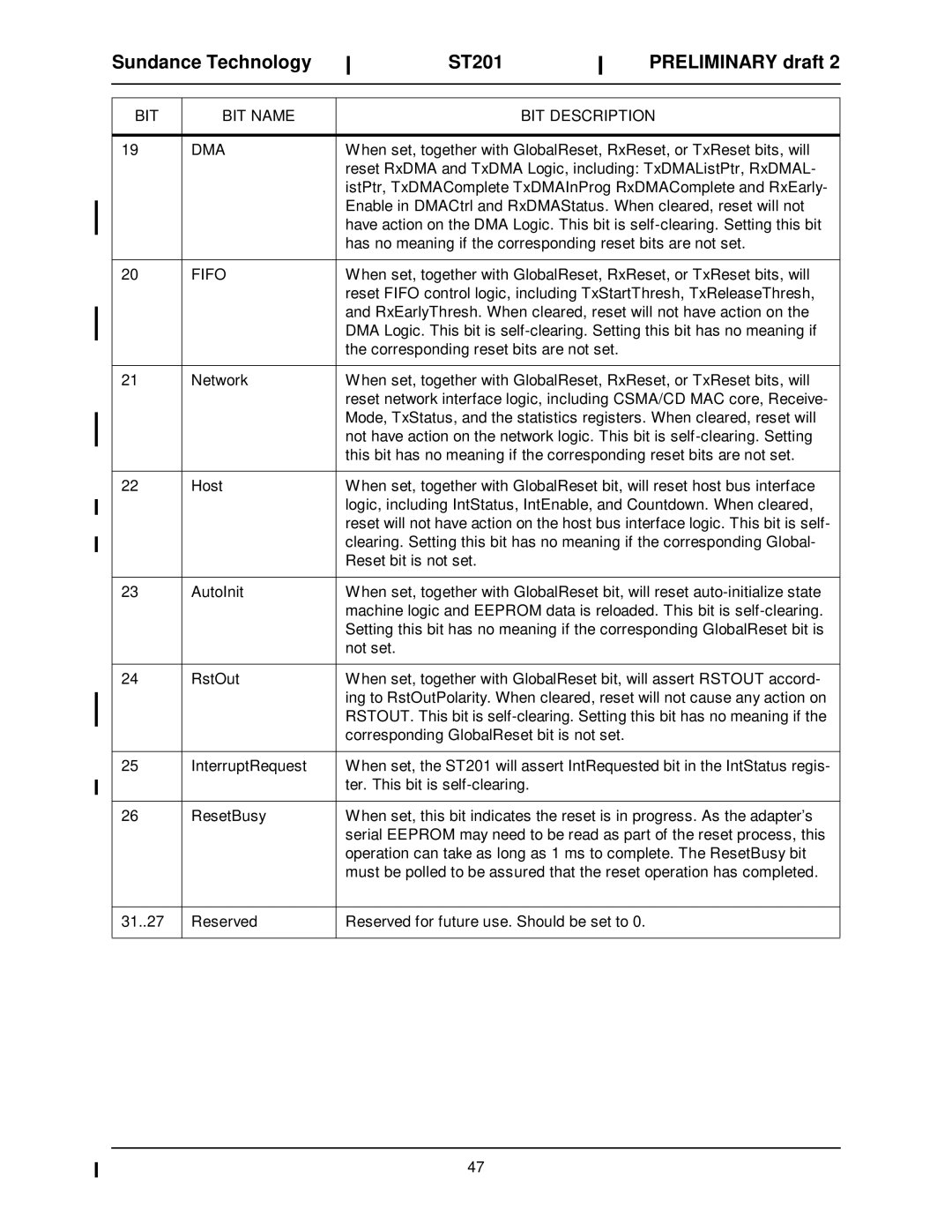

19DMA

20FIFO

21Network

22Host

23AutoInit

24RstOut

25InterruptRequest

26ResetBusy

31..27 | Reserved |

ST201 |

| PRELIMINARY draft 2 |

|

BIT DESCRIPTION

When set, together with GlobalReset, RxReset, or TxReset bits, will reset RxDMA and TxDMA Logic, including: TxDMAListPtr, RxDMAL- istPtr, TxDMAComplete TxDMAInProg RxDMAComplete and RxEarly- Enable in DMACtrl and RxDMAStatus. When cleared, reset will not have action on the DMA Logic. This bit is

When set, together with GlobalReset, RxReset, or TxReset bits, will reset FIFO control logic, including TxStartThresh, TxReleaseThresh, and RxEarlyThresh. When cleared, reset will not have action on the DMA Logic. This bit is

When set, together with GlobalReset, RxReset, or TxReset bits, will reset network interface logic, including CSMA/CD MAC core, Receive- Mode, TxStatus, and the statistics registers. When cleared, reset will not have action on the network logic. This bit is

When set, together with GlobalReset bit, will reset host bus interface logic, including IntStatus, IntEnable, and Countdown. When cleared, reset will not have action on the host bus interface logic. This bit is self- clearing. Setting this bit has no meaning if the corresponding Global- Reset bit is not set.

When set, together with GlobalReset bit, will reset

When set, together with GlobalReset bit, will assert RSTOUT accord- ing to RstOutPolarity. When cleared, reset will not cause any action on RSTOUT. This bit is

When set, the ST201 will assert IntRequested bit in the IntStatus regis- ter. This bit is

When set, this bit indicates the reset is in progress. As the adapter’s serial EEPROM may need to be read as part of the reset process, this operation can take as long as 1 ms to complete. The ResetBusy bit must be polled to be assured that the reset operation has completed.

Reserved for future use. Should be set to 0.

47