Sundance Technology

ST201

PRELIMINARY draft 2

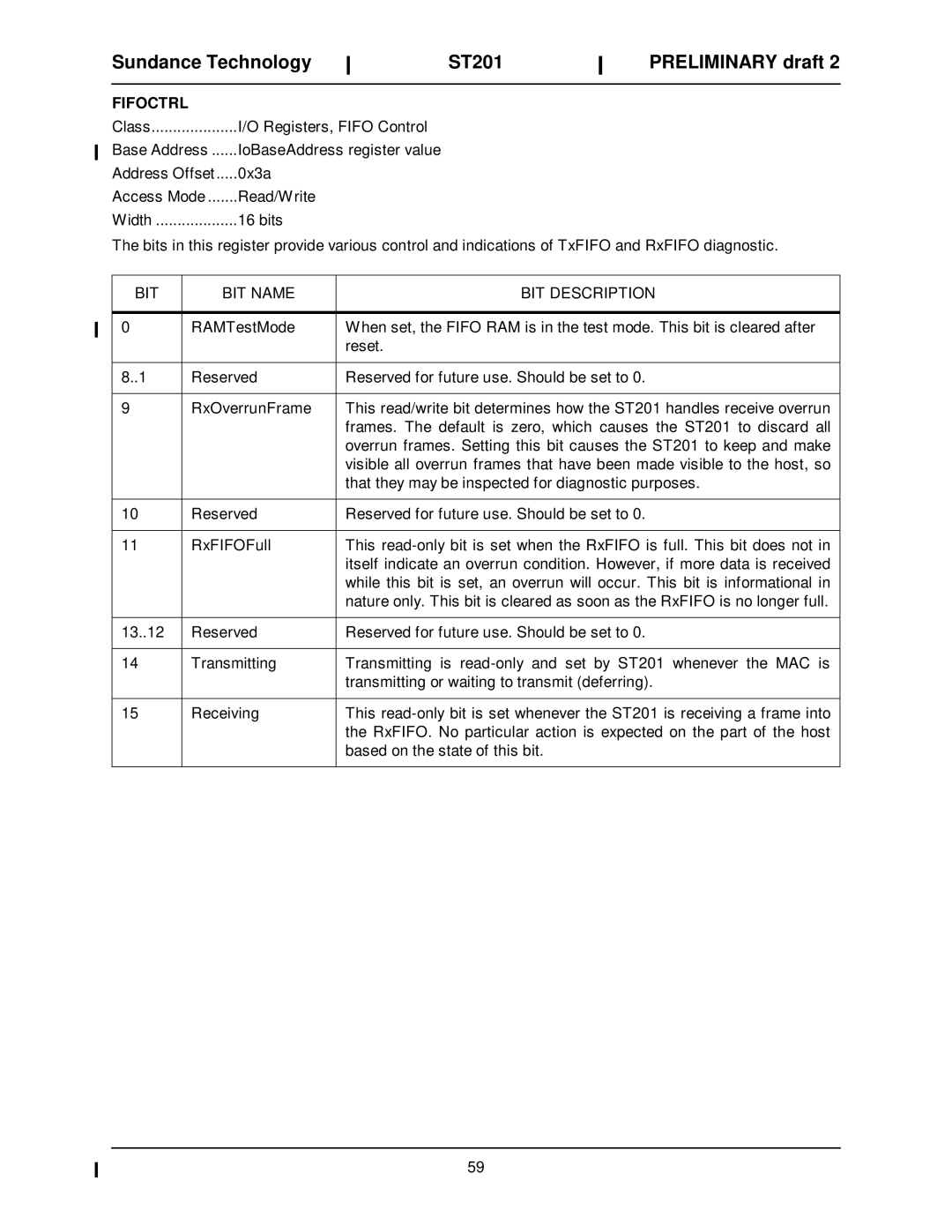

FIFOCTRL |

|

Class | I/O Registers, FIFO Control |

Base Address | IoBaseAddress register value |

Address Offset | 0x3a |

Access Mode | Read/Write |

Width | 16 bits |

The bits in this register provide various control and indications of TxFIFO and RxFIFO diagnostic.

BIT

0

8..1

9

10

11

13..12

14

15

BIT NAME

RAMTestMode

Reserved

RxOverrunFrame

Reserved

RxFIFOFull

Reserved

Transmitting

Receiving

BIT DESCRIPTION

When set, the FIFO RAM is in the test mode. This bit is cleared after reset.

Reserved for future use. Should be set to 0.

This read/write bit determines how the ST201 handles receive overrun frames. The default is zero, which causes the ST201 to discard all overrun frames. Setting this bit causes the ST201 to keep and make visible all overrun frames that have been made visible to the host, so that they may be inspected for diagnostic purposes.

Reserved for future use. Should be set to 0.

This

Reserved for future use. Should be set to 0.

Transmitting is

This

59