Sundance Technology

ST201

PRELIMINARY draft 2

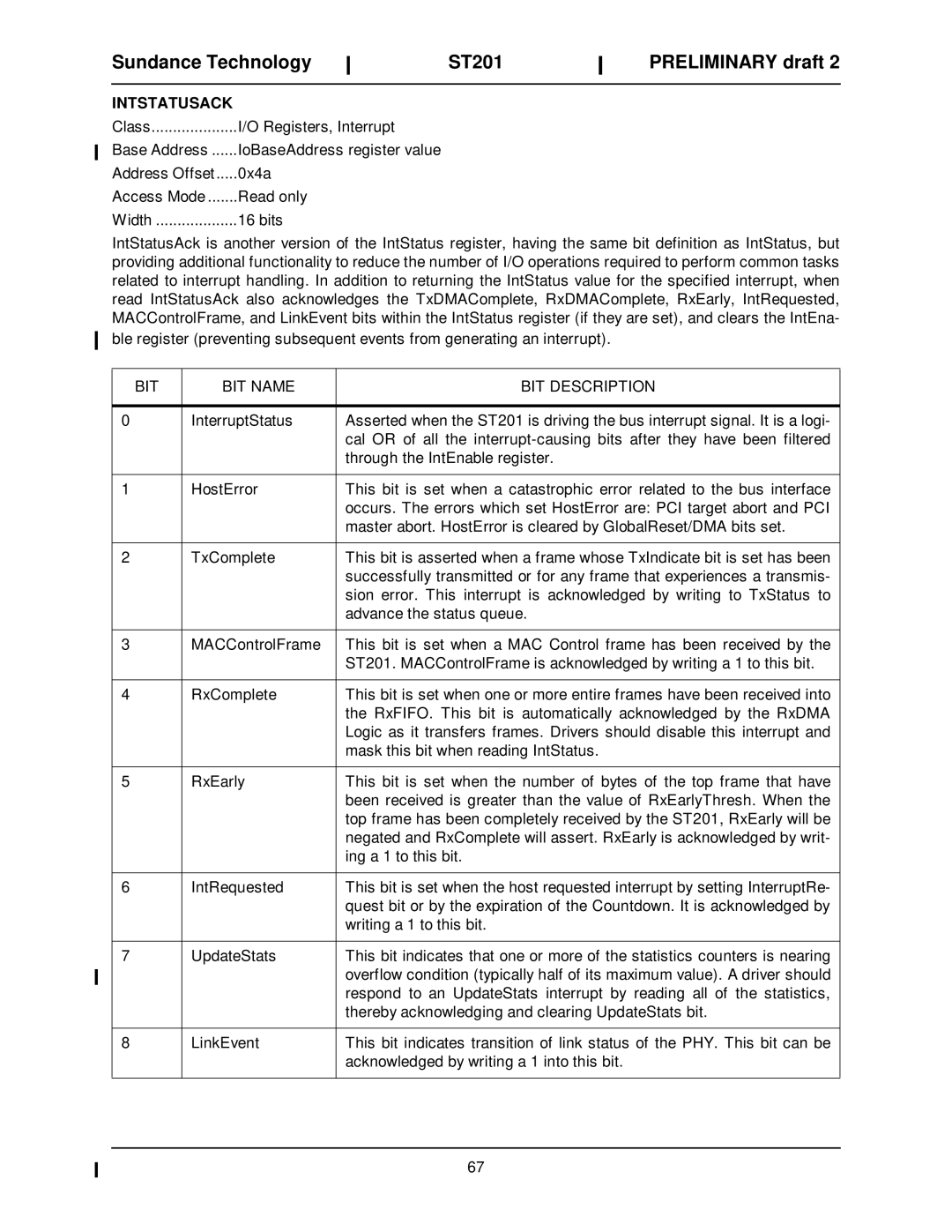

INTSTATUSACK |

|

Class | I/O Registers, Interrupt |

Base Address | IoBaseAddress register value |

Address Offset | 0x4a |

Access Mode | Read only |

Width | 16 bits |

IntStatusAck is another version of the IntStatus register, having the same bit definition as IntStatus, but providing additional functionality to reduce the number of I/O operations required to perform common tasks related to interrupt handling. In addition to returning the IntStatus value for the specified interrupt, when read IntStatusAck also acknowledges the TxDMAComplete, RxDMAComplete, RxEarly, IntRequested, MACControlFrame, and LinkEvent bits within the IntStatus register (if they are set), and clears the IntEna- ble register (preventing subsequent events from generating an interrupt).

BIT

0

1

2

3

4

5

6

7

8

BIT NAME

InterruptStatus

HostError

TxComplete

MACControlFrame

RxComplete

RxEarly

IntRequested

UpdateStats

LinkEvent

BIT DESCRIPTION

Asserted when the ST201 is driving the bus interrupt signal. It is a logi- cal OR of all the

This bit is set when a catastrophic error related to the bus interface occurs. The errors which set HostError are: PCI target abort and PCI master abort. HostError is cleared by GlobalReset/DMA bits set.

This bit is asserted when a frame whose TxIndicate bit is set has been successfully transmitted or for any frame that experiences a transmis- sion error. This interrupt is acknowledged by writing to TxStatus to advance the status queue.

This bit is set when a MAC Control frame has been received by the ST201. MACControlFrame is acknowledged by writing a 1 to this bit.

This bit is set when one or more entire frames have been received into the RxFIFO. This bit is automatically acknowledged by the RxDMA Logic as it transfers frames. Drivers should disable this interrupt and mask this bit when reading IntStatus.

This bit is set when the number of bytes of the top frame that have been received is greater than the value of RxEarlyThresh. When the top frame has been completely received by the ST201, RxEarly will be negated and RxComplete will assert. RxEarly is acknowledged by writ- ing a 1 to this bit.

This bit is set when the host requested interrupt by setting InterruptRe- quest bit or by the expiration of the Countdown. It is acknowledged by writing a 1 to this bit.

This bit indicates that one or more of the statistics counters is nearing overflow condition (typically half of its maximum value). A driver should respond to an UpdateStats interrupt by reading all of the statistics, thereby acknowledging and clearing UpdateStats bit.

This bit indicates transition of link status of the PHY. This bit can be acknowledged by writing a 1 into this bit.

67