Sundance Technology

ST201

PRELIMINARY draft 2

TXDMA AND FRAME TRANSMISSION

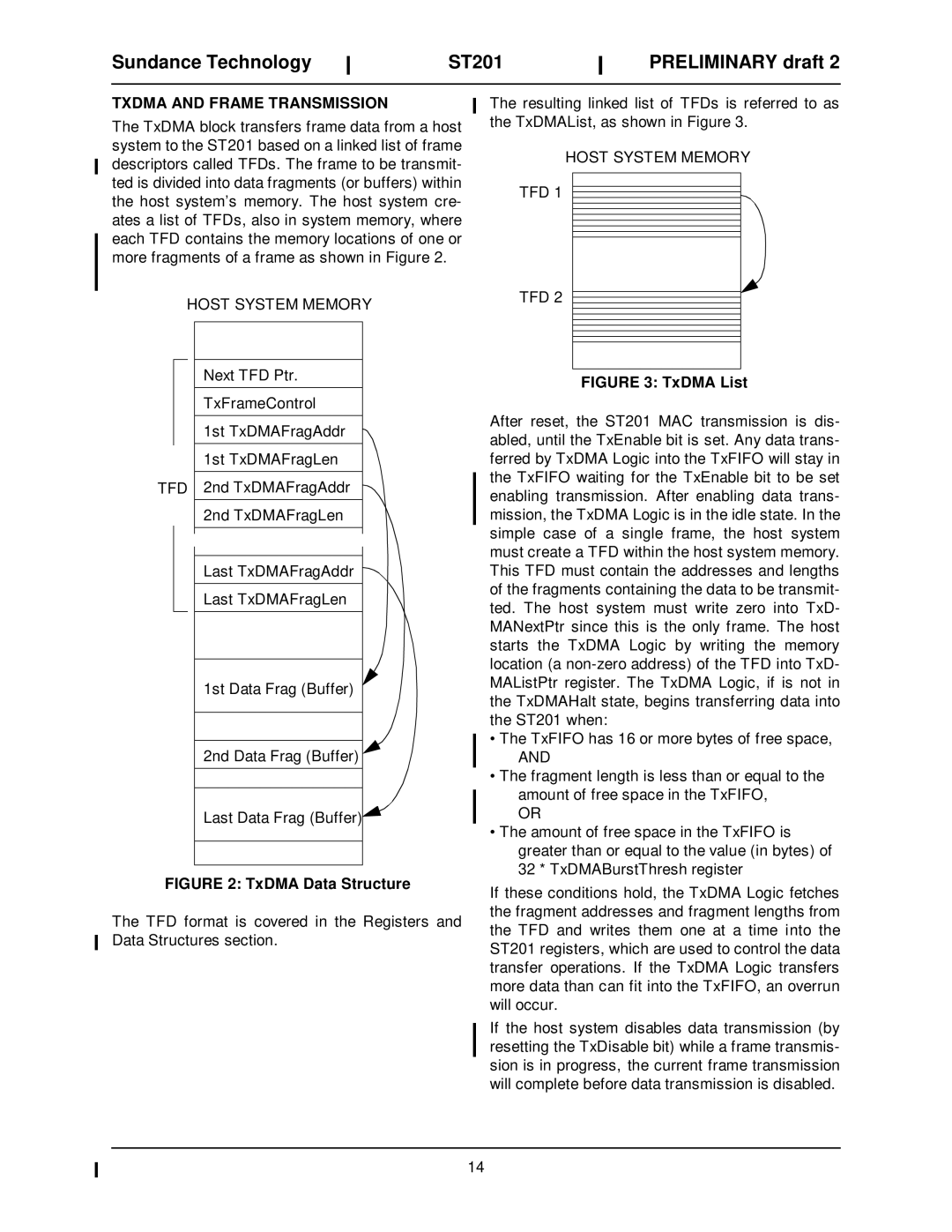

The TxDMA block transfers frame data from a host system to the ST201 based on a linked list of frame descriptors called TFDs. The frame to be transmit- ted is divided into data fragments (or buffers) within the host system’s memory. The host system cre- ates a list of TFDs, also in system memory, where each TFD contains the memory locations of one or more fragments of a frame as shown in Figure 2.

The resulting linked list of TFDs is referred to as the TxDMAList, as shown in Figure 3.

HOST SYSTEM MEMORY

TFD 1

HOST SYSTEM MEMORY

Next TFD Ptr.

TxFrameControl

1st TxDMAFragAddr

1st TxDMAFragLen

TFD 2nd TxDMAFragAddr

2nd TxDMAFragLen

Last TxDMAFragAddr

Last TxDMAFragLen

1st Data Frag (Buffer)

2nd Data Frag (Buffer)

Last Data Frag (Buffer)![]()

FIGURE 2: TxDMA Data Structure

The TFD format is covered in the Registers and Data Structures section.

TFD 2

FIGURE 3: TxDMA List

After reset, the ST201 MAC transmission is dis- abled, until the TxEnable bit is set. Any data trans- ferred by TxDMA Logic into the TxFIFO will stay in the TxFIFO waiting for the TxEnable bit to be set enabling transmission. After enabling data trans- mission, the TxDMA Logic is in the idle state. In the simple case of a single frame, the host system must create a TFD within the host system memory. This TFD must contain the addresses and lengths of the fragments containing the data to be transmit- ted. The host system must write zero into TxD- MANextPtr since this is the only frame. The host starts the TxDMA Logic by writing the memory location (a

•The TxFIFO has 16 or more bytes of free space,

AND

•The fragment length is less than or equal to the amount of free space in the TxFIFO,

OR

•The amount of free space in the TxFIFO is greater than or equal to the value (in bytes) of 32 * TxDMABurstThresh register

If these conditions hold, the TxDMA Logic fetches the fragment addresses and fragment lengths from the TFD and writes them one at a time into the ST201 registers, which are used to control the data transfer operations. If the TxDMA Logic transfers more data than can fit into the TxFIFO, an overrun will occur.

If the host system disables data transmission (by resetting the TxDisable bit) while a frame transmis- sion is in progress, the current frame transmission will complete before data transmission is disabled.

14