Sundance Technology

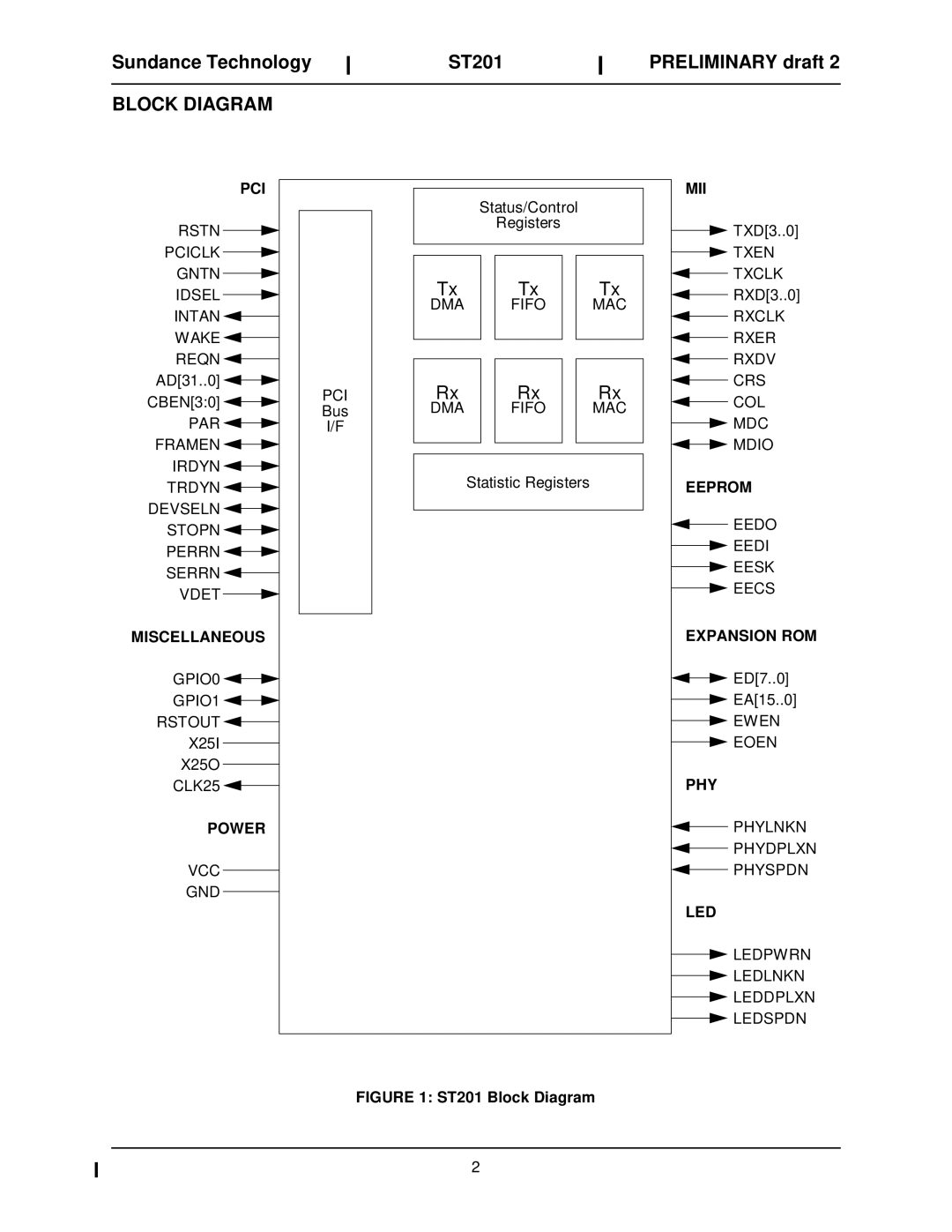

BLOCK DIAGRAM

ST201

PRELIMINARY draft 2

PCI

RSTN ![]()

![]() PCICLK

PCICLK ![]()

![]() GNTN

GNTN ![]()

![]() IDSEL

IDSEL ![]()

![]() INTAN

INTAN ![]() WAKE

WAKE ![]() REQN

REQN ![]() AD[31..0]

AD[31..0] ![]()

![]() CBEN[3:0]

CBEN[3:0] ![]()

![]()

PAR ![]()

![]() FRAMEN

FRAMEN ![]()

![]() IRDYN

IRDYN ![]()

![]() TRDYN

TRDYN ![]()

![]() DEVSELN

DEVSELN ![]()

![]() STOPN

STOPN ![]()

![]() PERRN

PERRN ![]()

![]() SERRN

SERRN ![]() VDET

VDET ![]()

![]()

MISCELLANEOUS

GPIO0 ![]()

![]() GPIO1

GPIO1 ![]()

![]()

RSTOUT ![]() X25I

X25I

X25O

CLK25 ![]()

POWER

VCC

GND

PCI Bus I/F

Status/Control

Registers

Tx |

| Tx |

| Tx |

DMA |

| FIFO |

| MAC |

|

|

|

|

|

Rx |

| Rx |

| Rx |

DMA |

| FIFO |

| MAC |

|

|

|

|

|

Statistic Registers

MII

![]()

![]() TXD[3..0]

TXD[3..0]

![]()

![]() TXEN

TXEN

![]() TXCLK

TXCLK

![]() RXD[3..0]

RXD[3..0]

![]() RXCLK

RXCLK

![]() RXER

RXER

![]() RXDV

RXDV

![]() CRS

CRS

![]() COL

COL

![]()

![]() MDC

MDC ![]()

![]() MDIO

MDIO

EEPROM

![]() EEDO

EEDO

![]()

![]() EEDI

EEDI

![]()

![]() EESK

EESK

![]()

![]() EECS

EECS

EXPANSION ROM

![]()

![]() ED[7..0]

ED[7..0]

![]()

![]() EA[15..0]

EA[15..0]

![]()

![]() EWEN

EWEN ![]()

![]() EOEN

EOEN

PHY

![]() PHYLNKN

PHYLNKN

![]() PHYDPLXN

PHYDPLXN ![]() PHYSPDN

PHYSPDN

LED

![]()

![]() LEDPWRN

LEDPWRN

![]()

![]() LEDLNKN

LEDLNKN

![]()

![]() LEDDPLXN

LEDDPLXN ![]()

![]() LEDSPDN

LEDSPDN

FIGURE 1: ST201 Block Diagram

2