Sundance Technology

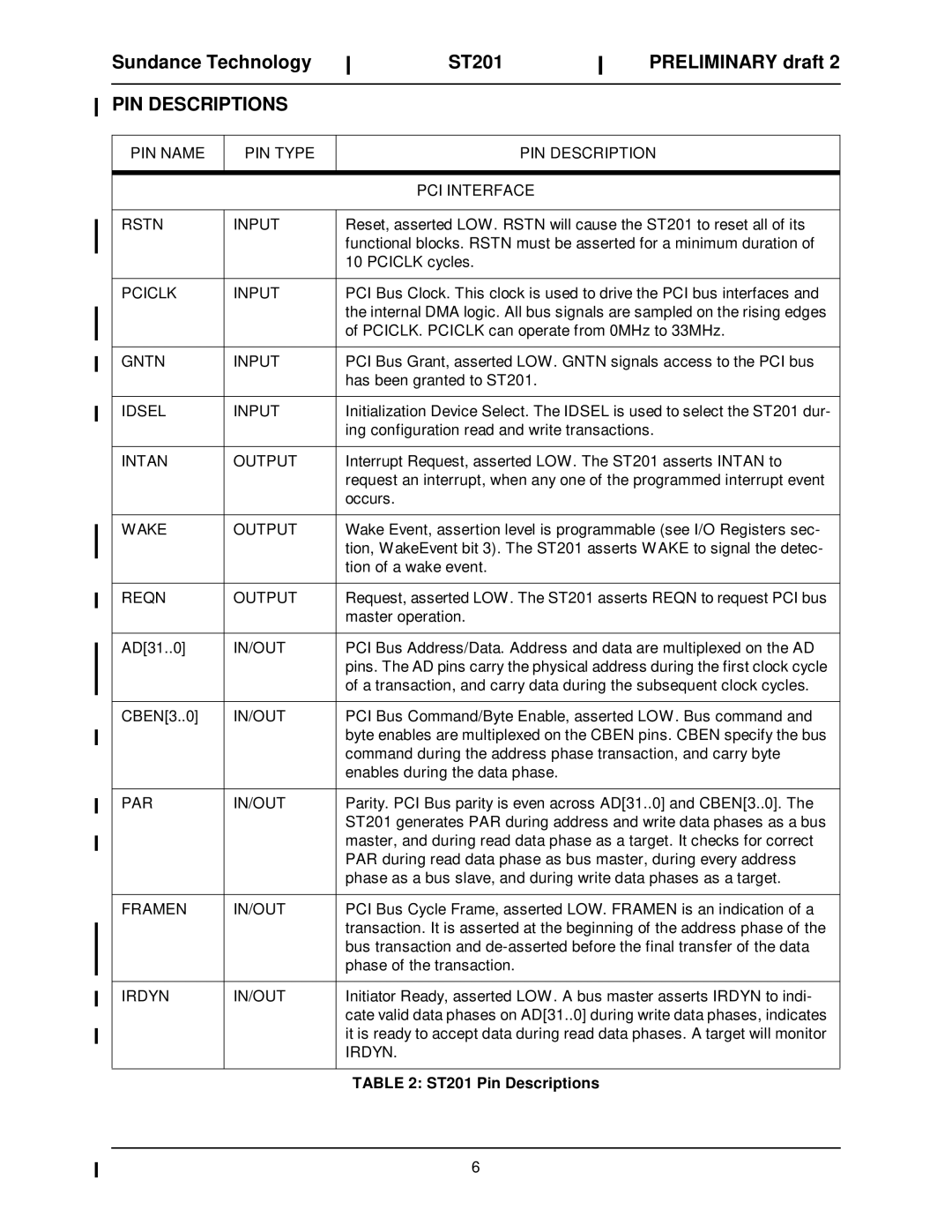

PIN DESCRIPTIONS

ST201

PRELIMINARY draft 2

PIN NAME

RSTN

PCICLK

GNTN

IDSEL

INTAN

WAKE

REQN

AD[31..0]

CBEN[3..0]

PAR

FRAMEN

IRDYN

PIN TYPE

INPUT

INPUT

INPUT

INPUT

OUTPUT

OUTPUT

OUTPUT

IN/OUT

IN/OUT

IN/OUT

IN/OUT

IN/OUT

PIN DESCRIPTION

PCI INTERFACE

Reset, asserted LOW. RSTN will cause the ST201 to reset all of its functional blocks. RSTN must be asserted for a minimum duration of 10 PCICLK cycles.

PCI Bus Clock. This clock is used to drive the PCI bus interfaces and the internal DMA logic. All bus signals are sampled on the rising edges of PCICLK. PCICLK can operate from 0MHz to 33MHz.

PCI Bus Grant, asserted LOW. GNTN signals access to the PCI bus has been granted to ST201.

Initialization Device Select. The IDSEL is used to select the ST201 dur- ing configuration read and write transactions.

Interrupt Request, asserted LOW. The ST201 asserts INTAN to request an interrupt, when any one of the programmed interrupt event occurs.

Wake Event, assertion level is programmable (see I/O Registers sec- tion, WakeEvent bit 3). The ST201 asserts WAKE to signal the detec- tion of a wake event.

Request, asserted LOW. The ST201 asserts REQN to request PCI bus master operation.

PCI Bus Address/Data. Address and data are multiplexed on the AD pins. The AD pins carry the physical address during the first clock cycle of a transaction, and carry data during the subsequent clock cycles.

PCI Bus Command/Byte Enable, asserted LOW. Bus command and byte enables are multiplexed on the CBEN pins. CBEN specify the bus command during the address phase transaction, and carry byte enables during the data phase.

Parity. PCI Bus parity is even across AD[31..0] and CBEN[3..0]. The ST201 generates PAR during address and write data phases as a bus master, and during read data phase as a target. It checks for correct PAR during read data phase as bus master, during every address phase as a bus slave, and during write data phases as a target.

PCI Bus Cycle Frame, asserted LOW. FRAMEN is an indication of a transaction. It is asserted at the beginning of the address phase of the bus transaction and

Initiator Ready, asserted LOW. A bus master asserts IRDYN to indi- cate valid data phases on AD[31..0] during write data phases, indicates it is ready to accept data during read data phases. A target will monitor

IRDYN.

TABLE 2: ST201 Pin Descriptions

6