Sundance Technology

ST201 |

| PRELIMINARY draft 2 |

|

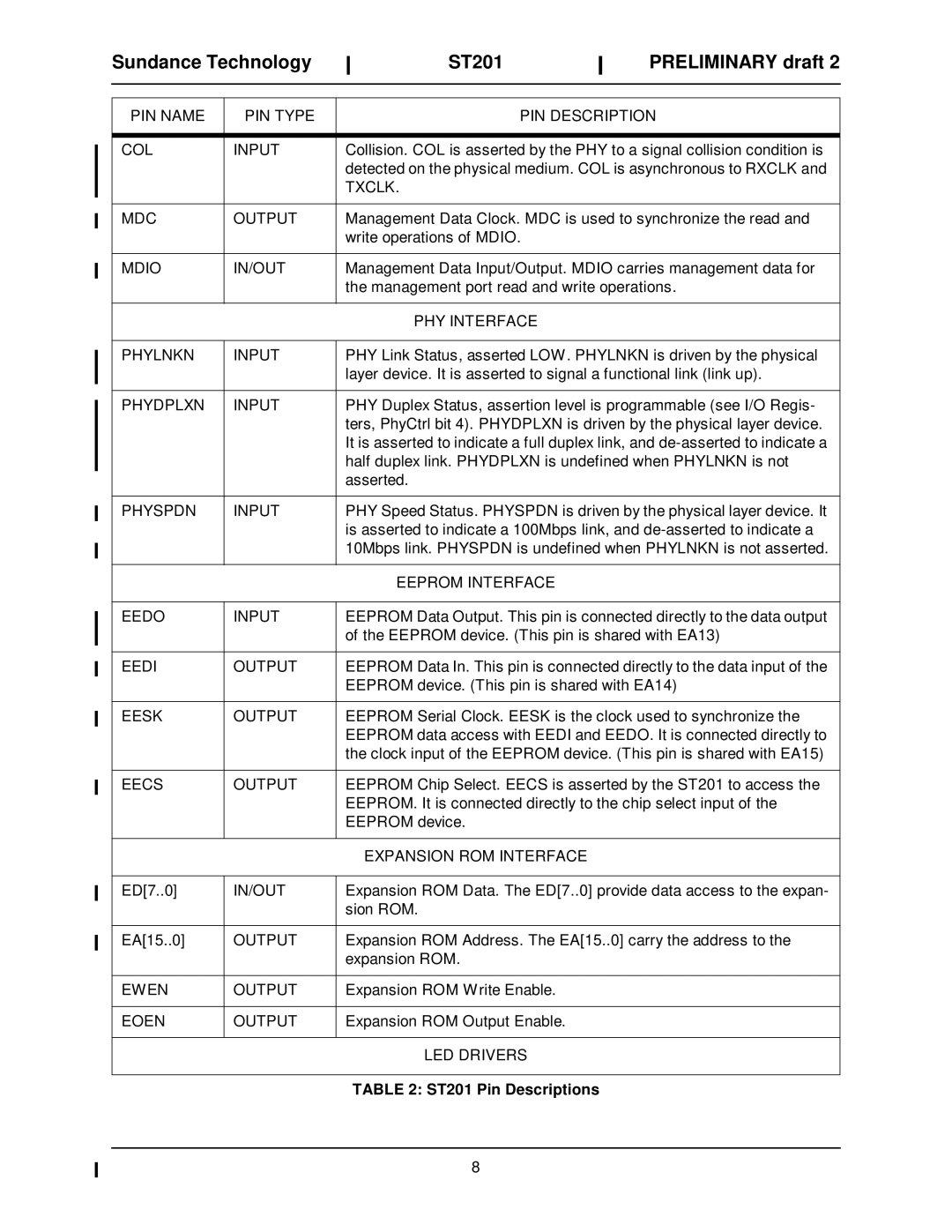

PIN NAME COL

MDC

MDIO

PHYLNKN

PHYDPLXN

PHYSPDN

EEDO

EEDI

EESK

EECS

ED[7..0]

EA[15..0]

EWEN

EOEN

PIN TYPE INPUT

OUTPUT

IN/OUT

INPUT

INPUT

INPUT

INPUT

OUTPUT

OUTPUT

OUTPUT

IN/OUT

OUTPUT

OUTPUT OUTPUT

PIN DESCRIPTION

Collision. COL is asserted by the PHY to a signal collision condition is detected on the physical medium. COL is asynchronous to RXCLK and

TXCLK.

Management Data Clock. MDC is used to synchronize the read and write operations of MDIO.

Management Data Input/Output. MDIO carries management data for the management port read and write operations.

PHY INTERFACE

PHY Link Status, asserted LOW. PHYLNKN is driven by the physical layer device. It is asserted to signal a functional link (link up).

PHY Duplex Status, assertion level is programmable (see I/O Regis- ters, PhyCtrl bit 4). PHYDPLXN is driven by the physical layer device. It is asserted to indicate a full duplex link, and

PHY Speed Status. PHYSPDN is driven by the physical layer device. It is asserted to indicate a 100Mbps link, and

EEPROM INTERFACE

EEPROM Data Output. This pin is connected directly to the data output of the EEPROM device. (This pin is shared with EA13)

EEPROM Data In. This pin is connected directly to the data input of the EEPROM device. (This pin is shared with EA14)

EEPROM Serial Clock. EESK is the clock used to synchronize the EEPROM data access with EEDI and EEDO. It is connected directly to the clock input of the EEPROM device. (This pin is shared with EA15)

EEPROM Chip Select. EECS is asserted by the ST201 to access the EEPROM. It is connected directly to the chip select input of the EEPROM device.

EXPANSION ROM INTERFACE

Expansion ROM Data. The ED[7..0] provide data access to the expan- sion ROM.

Expansion ROM Address. The EA[15..0] carry the address to the expansion ROM.

Expansion ROM Write Enable.

Expansion ROM Output Enable.

LED DRIVERS

TABLE 2: ST201 Pin Descriptions

8