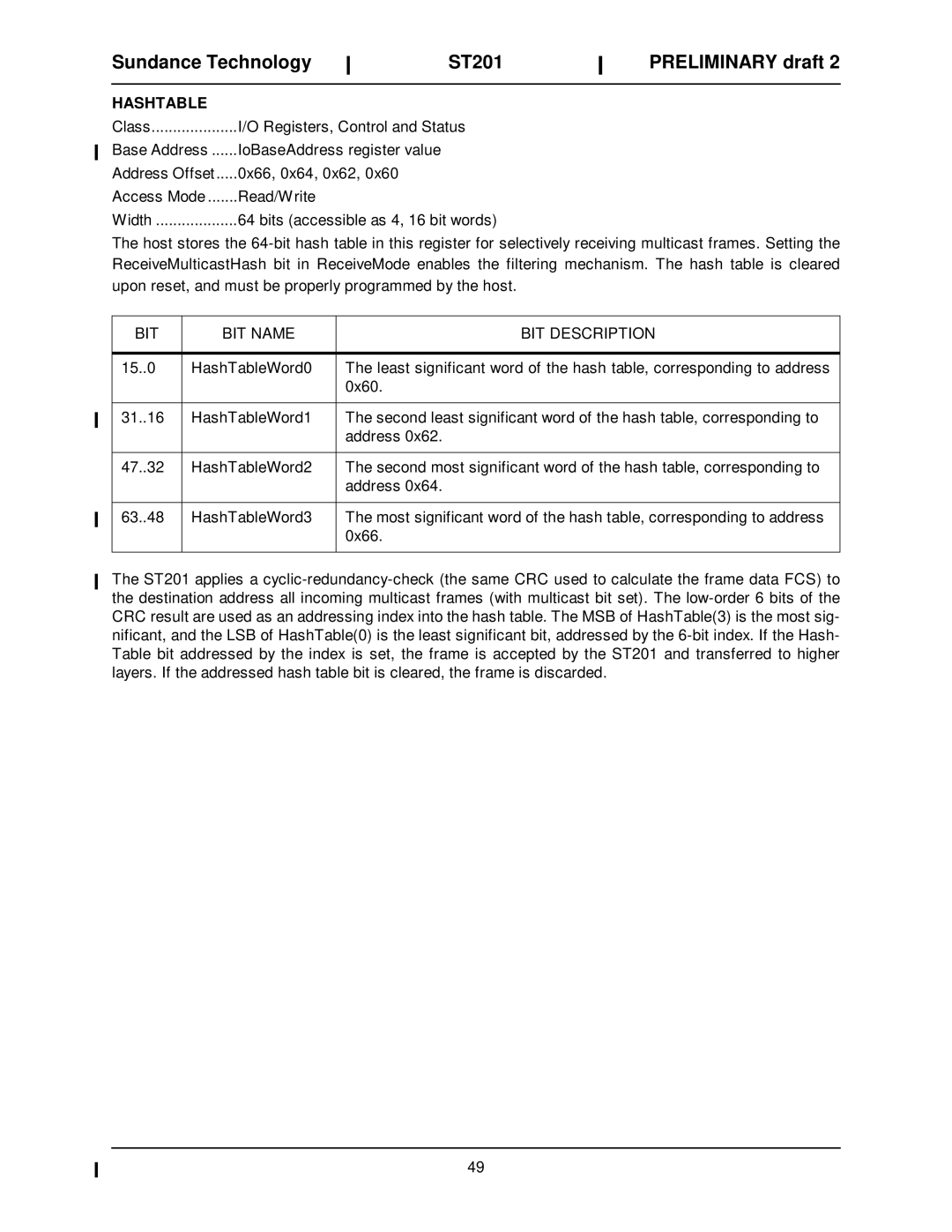

HASHTABLE | |

Class | I/O Registers, Control and Status |

Base Address | IoBaseAddress register value |

Address Offset | 0x66, 0x64, 0x62, 0x60 |

Access Mode | Read/Write |

Width | 64 bits (accessible as 4, 16 bit words) |

The host stores the 64-bit hash table in this register for selectively receiving multicast frames. Setting the ReceiveMulticastHash bit in ReceiveMode enables the filtering mechanism. The hash table is cleared upon reset, and must be properly programmed by the host.

BIT

15..0

31..16

47..32

63..48

BIT NAME

HashTableWord0

HashTableWord1

HashTableWord2

HashTableWord3

BIT DESCRIPTION

The least significant word of the hash table, corresponding to address 0x60.

The second least significant word of the hash table, corresponding to address 0x62.

The second most significant word of the hash table, corresponding to address 0x64.

The most significant word of the hash table, corresponding to address 0x66.

The ST201 applies a cyclic-redundancy-check (the same CRC used to calculate the frame data FCS) to the destination address all incoming multicast frames (with multicast bit set). The low-order 6 bits of the CRC result are used as an addressing index into the hash table. The MSB of HashTable(3) is the most sig- nificant, and the LSB of HashTable(0) is the least significant bit, addressed by the 6-bit index. If the Hash- Table bit addressed by the index is set, the frame is accepted by the ST201 and transferred to higher layers. If the addressed hash table bit is cleared, the frame is discarded.