186 |

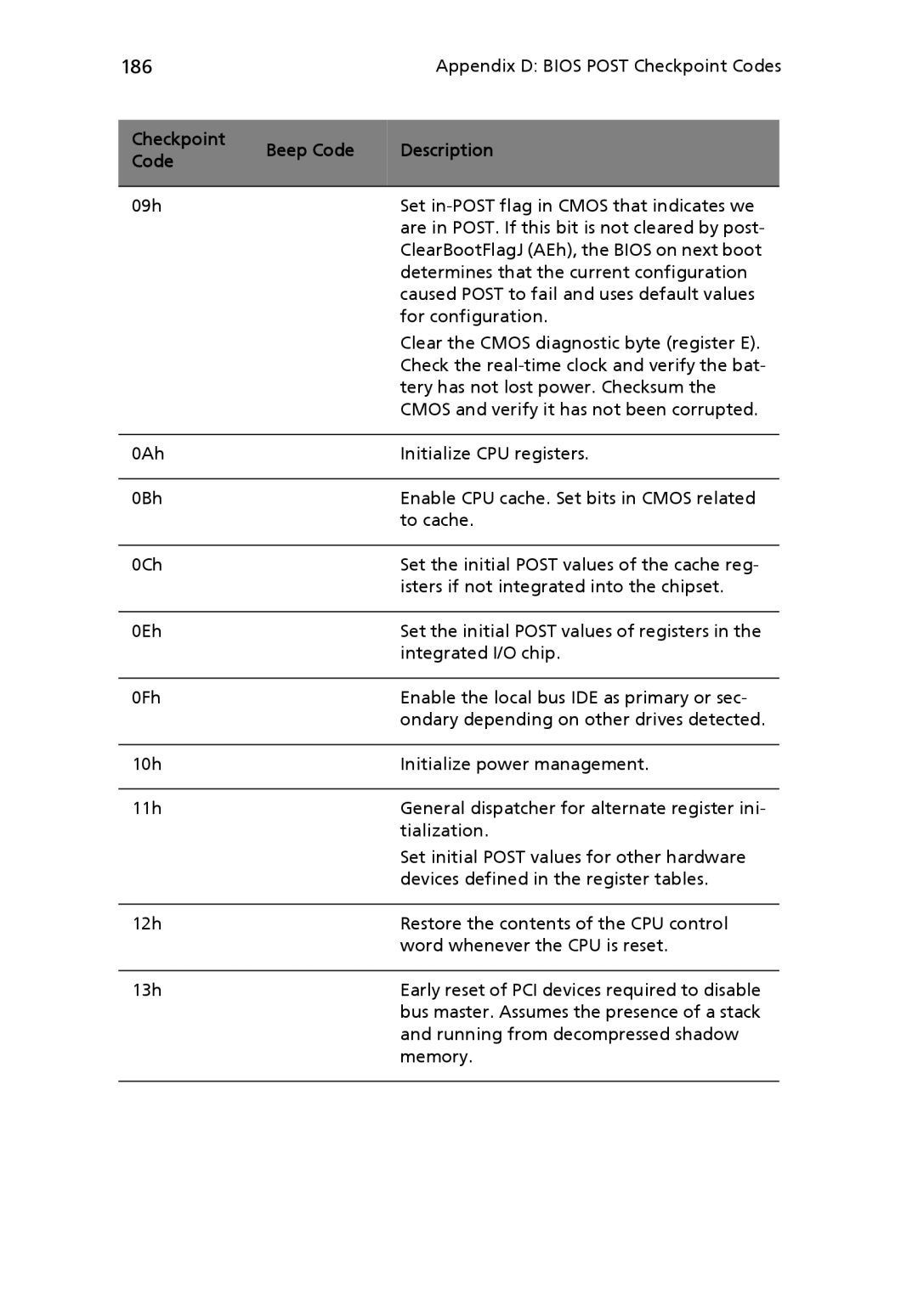

| Appendix D: BIOS POST Checkpoint Codes | |

|

|

| |

Checkpoint | Beep Code | Description | |

Code | |||

|

| ||

|

|

| |

09h |

| Set | |

|

| are in POST. If this bit is not cleared by post- | |

|

| ClearBootFlagJ (AEh), the BIOS on next boot | |

|

| determines that the current configuration | |

|

| caused POST to fail and uses default values | |

|

| for configuration. | |

|

| Clear the CMOS diagnostic byte (register E). | |

|

| Check the | |

|

| tery has not lost power. Checksum the | |

|

| CMOS and verify it has not been corrupted. | |

|

|

| |

0Ah |

| Initialize CPU registers. | |

|

|

| |

0Bh |

| Enable CPU cache. Set bits in CMOS related | |

|

| to cache. | |

|

|

| |

0Ch |

| Set the initial POST values of the cache reg- | |

|

| isters if not integrated into the chipset. | |

|

|

| |

0Eh |

| Set the initial POST values of registers in the | |

|

| integrated I/O chip. | |

|

|

| |

0Fh |

| Enable the local bus IDE as primary or sec- | |

|

| ondary depending on other drives detected. | |

|

|

| |

10h |

| Initialize power management. | |

|

|

| |

11h |

| General dispatcher for alternate register ini- | |

|

| tialization. | |

|

| Set initial POST values for other hardware | |

|

| devices defined in the register tables. | |

|

|

| |

12h |

| Restore the contents of the CPU control | |

|

| word whenever the CPU is reset. | |

|

|

| |

13h |

| Early reset of PCI devices required to disable | |

|

| bus master. Assumes the presence of a stack | |

|

| and running from decompressed shadow | |

|

| memory. | |

|

|

|

Page 198

Image 198