|

| 191 | |

|

|

| |

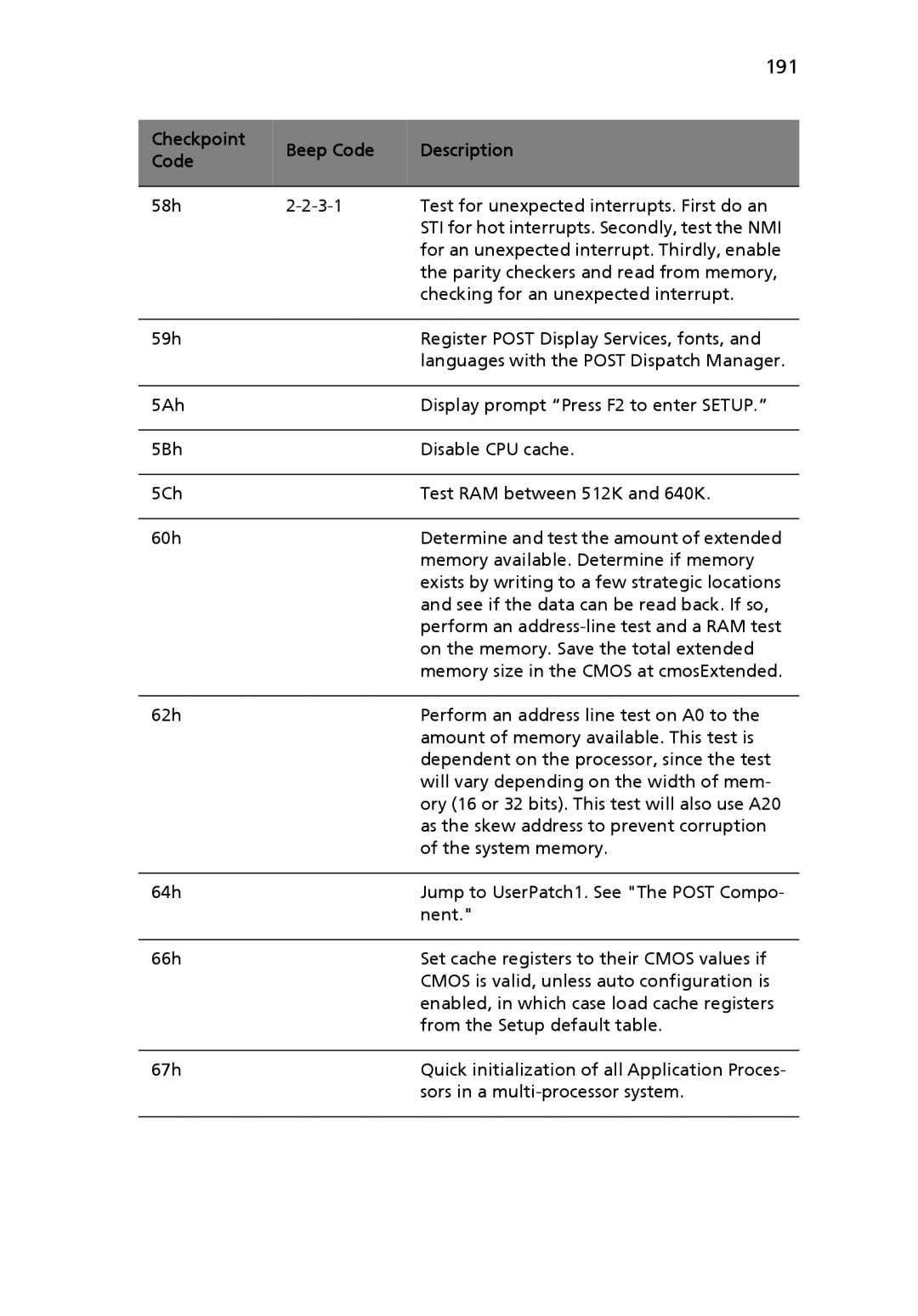

Checkpoint | Beep Code | Description | |

Code | |||

|

| ||

|

|

| |

58h | Test for unexpected interrupts. First do an | ||

|

| STI for hot interrupts. Secondly, test the NMI | |

|

| for an unexpected interrupt. Thirdly, enable | |

|

| the parity checkers and read from memory, | |

|

| checking for an unexpected interrupt. | |

|

|

| |

59h |

| Register POST Display Services, fonts, and | |

|

| languages with the POST Dispatch Manager. | |

|

|

| |

5Ah |

| Display prompt “Press F2 to enter SETUP.” | |

|

|

| |

5Bh |

| Disable CPU cache. | |

|

|

| |

5Ch |

| Test RAM between 512K and 640K. | |

|

|

| |

60h |

| Determine and test the amount of extended | |

|

| memory available. Determine if memory | |

|

| exists by writing to a few strategic locations | |

|

| and see if the data can be read back. If so, | |

|

| perform an | |

|

| on the memory. Save the total extended | |

|

| memory size in the CMOS at cmosExtended. | |

|

|

| |

62h |

| Perform an address line test on A0 to the | |

|

| amount of memory available. This test is | |

|

| dependent on the processor, since the test | |

|

| will vary depending on the width of mem- | |

|

| ory (16 or 32 bits). This test will also use A20 | |

|

| as the skew address to prevent corruption | |

|

| of the system memory. | |

|

|

| |

64h |

| Jump to UserPatch1. See "The POST Compo- | |

|

| nent." | |

|

|

| |

66h |

| Set cache registers to their CMOS values if | |

|

| CMOS is valid, unless auto configuration is | |

|

| enabled, in which case load cache registers | |

|

| from the Setup default table. | |

|

|

| |

67h |

| Quick initialization of all Application Proces- | |

|

| sors in a | |

|

|

|

Page 203

Image 203