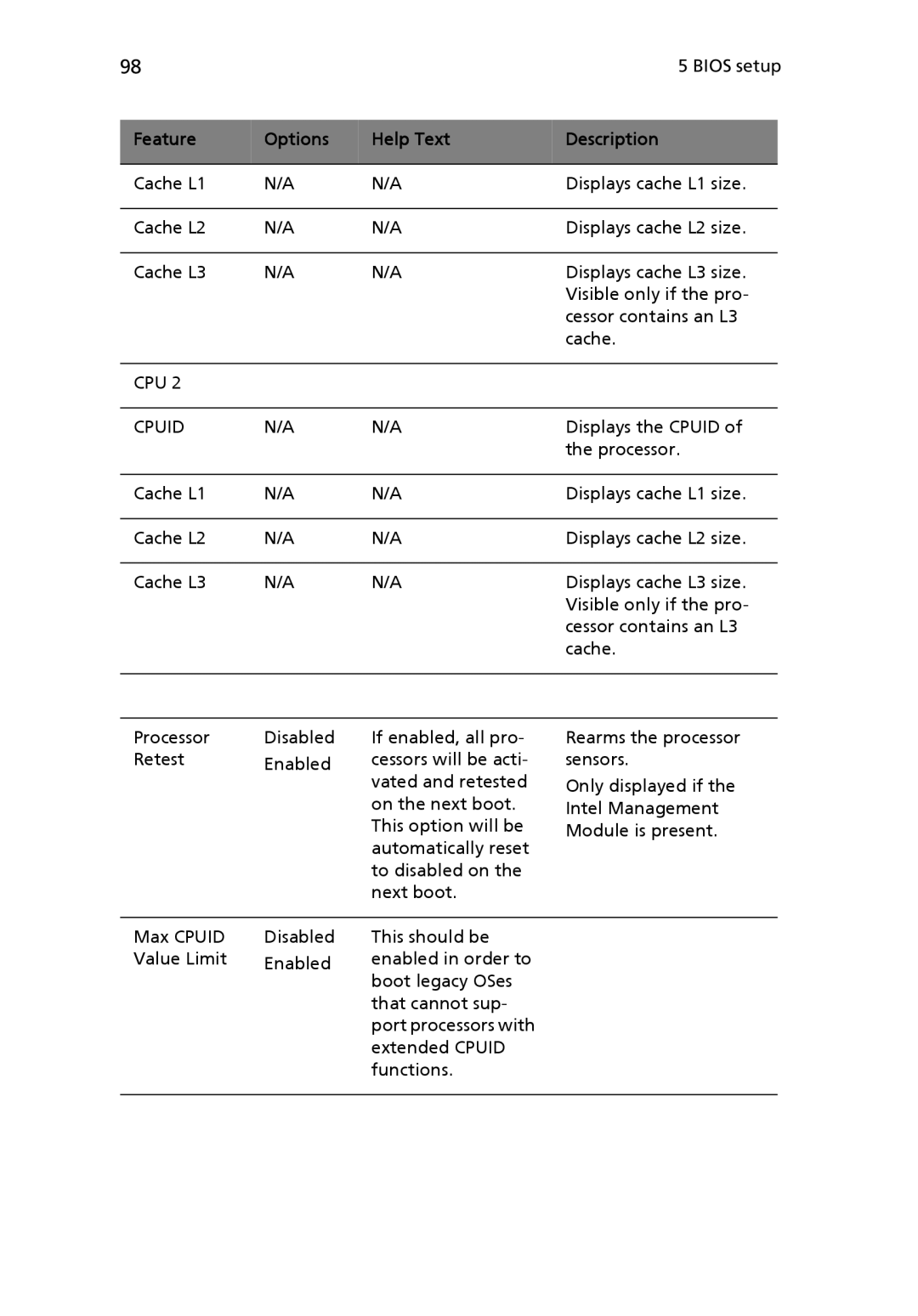

98 | 5 BIOS setup |

Feature | Options | Help Text | Description |

|

|

|

|

Cache L1 | N/A | N/A | Displays cache L1 size. |

|

|

|

|

Cache L2 | N/A | N/A | Displays cache L2 size. |

|

|

|

|

Cache L3 | N/A | N/A | Displays cache L3 size. |

|

|

| Visible only if the pro- |

|

|

| cessor contains an L3 |

|

|

| cache. |

|

|

|

|

CPU 2 |

|

|

|

|

|

|

|

CPUID | N/A | N/A | Displays the CPUID of |

|

|

| the processor. |

|

|

|

|

Cache L1 | N/A | N/A | Displays cache L1 size. |

|

|

|

|

Cache L2 | N/A | N/A | Displays cache L2 size. |

|

|

|

|

Cache L3 | N/A | N/A | Displays cache L3 size. |

|

|

| Visible only if the pro- |

|

|

| cessor contains an L3 |

|

|

| cache. |

|

|

|

|

Processor Retest

Disabled | If enabled, all pro- |

Enabled | cessors will be acti- |

| vated and retested |

| on the next boot. |

| This option will be |

| automatically reset |

| to disabled on the |

| next boot. |

Rearms the processor sensors.

Only displayed if the Intel Management Module is present.

Max CPUID Value Limit

Disabled | This should be |

Enabled | enabled in order to |

| boot legacy OSes |

| that cannot sup- |

| port processors with |

| extended CPUID |

| functions. |