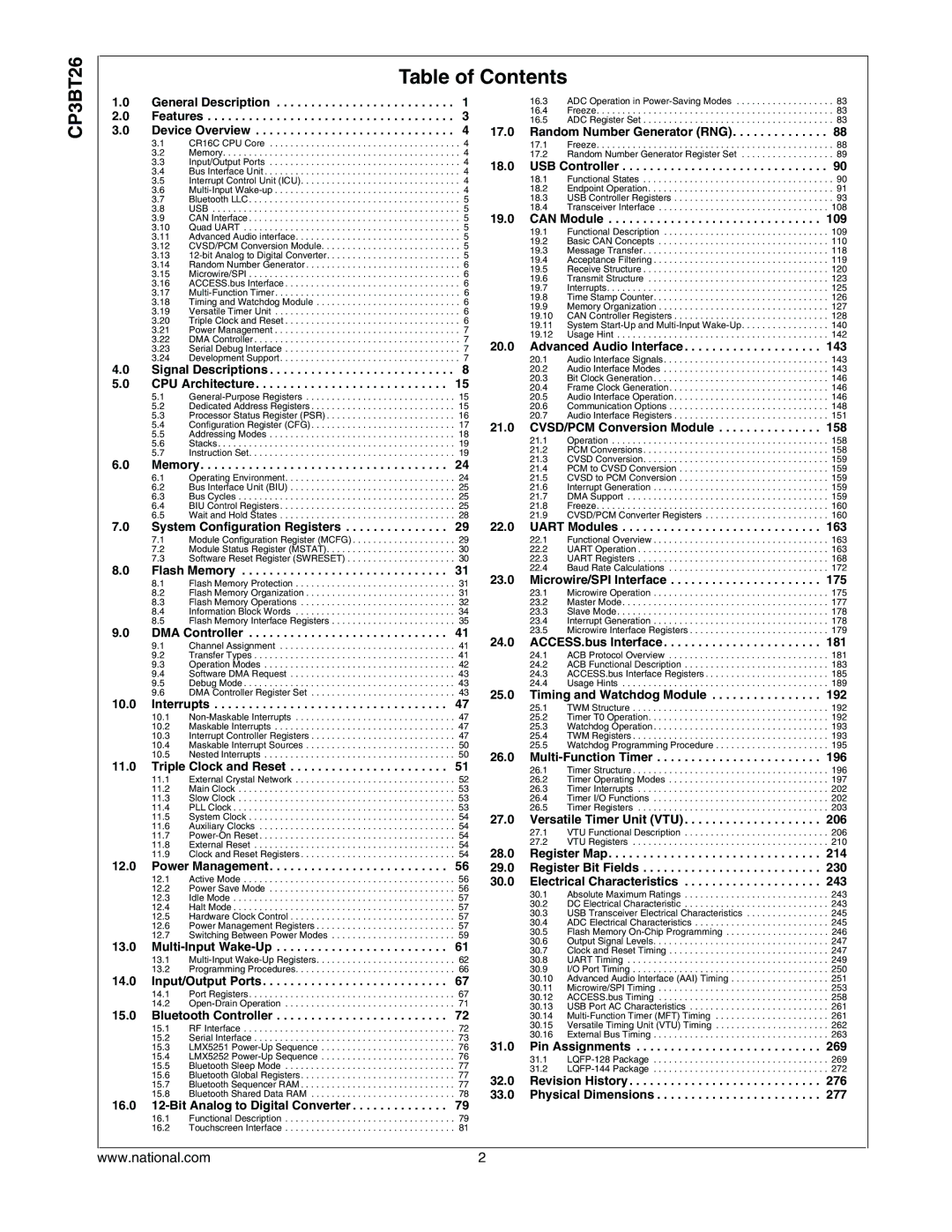

Table of Contents

CP3BT26

1.0 General Description . . . . . . . . . . . . . . . . . . . . . . . . . . 1

2.0 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

3.0 Device Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

3.1 CR16C CPU Core . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

3.2 Memory. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

3.3 Input/Output Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

3.4 Bus Interface Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

3.5 Interrupt Control Unit (ICU). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

3.6

3.7 Bluetooth LLC. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

3.8 USB . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

3.9 CAN Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

3.10 Quad UART . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

3.11 Advanced Audio interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

3.12 CVSD/PCM Conversion Module. . . . . . . . . . . . . . . . . . . . . . . . . . . 5

3.13

3.14 Random Number Generator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

3.15 Microwire/SPI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

3.16 ACCESS.bus Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

3.17

3.18 Timing and Watchdog Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

3.19 Versatile Timer Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

3.20 Triple Clock and Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

3.21 Power Management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

3.22 DMA Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

3.23 Serial Debug Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

3.24 Development Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

4.0 | Signal Descriptions | 8 | |

5.0 | CPU Architecture | 15 | |

| 5.1 | 15 | |

| 5.2 | Dedicated Address Registers | 15 |

| 5.3 | Processor Status Register (PSR) | 16 |

| 5.4 | Configuration Register (CFG) | 17 |

| 5.5 | Addressing Modes | 18 |

| 5.6 | Stacks | 19 |

| 5.7 | Instruction Set | 19 |

6.0 Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

6.1 Operating Environment. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

6.2 Bus Interface Unit (BIU) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

6.3 Bus Cycles . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

6.4 BIU Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

6.5 Wait and Hold States . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

7.0 System Configuration Registers . . . . . . . . . . . . . . . 29

7.1 Module Configuration Register (MCFG) . . . . . . . . . . . . . . . . . . . . 29

7.2 Module Status Register (MSTAT). . . . . . . . . . . . . . . . . . . . . . . . . 30

7.3 Software Reset Register (SWRESET) . . . . . . . . . . . . . . . . . . . . . 30

8.0 Flash Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

8.1 Flash Memory Protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

8.2 Flash Memory Organization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

8.3 Flash Memory Operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

8.4 Information Block Words . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

8.5 Flash Memory Interface Registers . . . . . . . . . . . . . . . . . . . . . . . . 35

9.0 DMA Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

9.1 Channel Assignment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

9.2 Transfer Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

9.3 Operation Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

9.4 Software DMA Request . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

9.5 Debug Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

9.6 DMA Controller Register Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

10.0 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

10.1

10.2 Maskable Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

10.3 Interrupt Controller Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

10.4 Maskable Interrupt Sources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

10.5 Nested Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

11.0 Triple Clock and Reset . . . . . . . . . . . . . . . . . . . . . . . 51

11.1 External Crystal Network . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

11.2 Main Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

11.3 Slow Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

11.4 PLL Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

11.5 System Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

11.6 Auxiliary Clocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

11.7

11.8 External Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

11.9 Clock and Reset Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

12.0 Power Management . . . . . . . . . . . . . . . . . . . . . . . . . . 56

12.1 Active Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

12.2 Power Save Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

12.3 Idle Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

12.4 Halt Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

12.5 Hardware Clock Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

12.6 Power Management Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

12.7 Switching Between Power Modes . . . . . . . . . . . . . . . . . . . . . . . . 59

13.0

13.1

13.2 Programming Procedures. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

14.0 Input/Output Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

14.1 Port Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

14.2

15.0 Bluetooth Controller . . . . . . . . . . . . . . . . . . . . . . . . . 72

15.1 RF Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

15.2 Serial Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

15.3 LMX5251

15.4 LMX5252

15.5 Bluetooth Sleep Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

15.6 Bluetooth Global Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

15.7 Bluetooth Sequencer RAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

15.8 Bluetooth Shared Data RAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

16.0

16.1 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

16.2 Touchscreen Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

16.3 ADC Operation in

16.4 Freeze. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

16.5 ADC Register Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

17.0 Random Number Generator (RNG). . . . . . . . . . . . . . 88

17.1 Freeze. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

17.2 Random Number Generator Register Set . . . . . . . . . . . . . . . . . . 89

18.0 USB Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

18.1 Functional States . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

18.2 Endpoint Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

18.3 USB Controller Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

18.4 Transceiver Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

19.0 CAN Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

19.1 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

19.2 Basic CAN Concepts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

19.3 Message Transfer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

19.4 Acceptance Filtering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

19.5 Receive Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

19.6 Transmit Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

19.7 Interrupts. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

19.8 Time Stamp Counter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

19.9 Memory Organization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

19.10 CAN Controller Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

19.11 System

19.12 Usage Hint . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 142

20.0 Advanced Audio Interface . . . . . . . . . . . . . . . . . . . . 143

20.1 Audio Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 143

20.2 Audio Interface Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 143

20.3 Bit Clock Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 146

20.4 Frame Clock Generation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 146

20.5 Audio Interface Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 146

20.6 Communication Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 148

20.7 Audio Interface Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 151

21.0 CVSD/PCM Conversion Module . . . . . . . . . . . . . . . 158

21.1 Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 158

21.2 PCM Conversions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 158

21.3 CVSD Conversion. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 159

21.4 PCM to CVSD Conversion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 159

21.5 CVSD to PCM Conversion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 159

21.6 Interrupt Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 159

21.7 DMA Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 159

21.8 Freeze. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 160

21.9 CVSD/PCM Converter Registers . . . . . . . . . . . . . . . . . . . . . . . . 160

22.0 UART Modules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 163

22.1 Functional Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 163

22.2 UART Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 163

22.3 UART Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 168

22.4 Baud Rate Calculations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 172

23.0 Microwire/SPI Interface . . . . . . . . . . . . . . . . . . . . . . 175

23.1 Microwire Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 175

23.2 Master Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 177

23.3 Slave Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 178

23.4 Interrupt Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 178

23.5 Microwire Interface Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . 179

24.0 ACCESS.bus Interface . . . . . . . . . . . . . . . . . . . . . . . 181

24.1 ACB Protocol Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 181

24.2 ACB Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . 183

24.3 ACCESS.bus Interface Registers . . . . . . . . . . . . . . . . . . . . . . . . 185

24.4 Usage Hints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 189

25.0 Timing and Watchdog Module . . . . . . . . . . . . . . . . 192

25.1 TWM Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 192

25.2 Timer T0 Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 192

25.3 Watchdog Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 193

25.4 TWM Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 193

25.5 Watchdog Programming Procedure . . . . . . . . . . . . . . . . . . . . . . 195

26.0

26.1 Timer Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 196

26.2 Timer Operating Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 197

26.3 Timer Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 202

26.4 Timer I/O Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 202

26.5 Timer Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 203

27.0 Versatile Timer Unit (VTU) . . . . . . . . . . . . . . . . . . . . 206

27.1 VTU Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . 206

27.2 VTU Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 210

28.0 Register Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 214

29.0 Register Bit Fields . . . . . . . . . . . . . . . . . . . . . . . . . . 230

30.0 Electrical Characteristics . . . . . . . . . . . . . . . . . . . . 243

30.1 Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . 243

30.2 DC Electrical Characteristic . . . . . . . . . . . . . . . . . . . . . . . . . . . . 243

30.3 USB Transceiver Electrical Characteristics . . . . . . . . . . . . . . . . 245

30.4 ADC Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . 245

30.5 Flash Memory

30.6 Output Signal Levels. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 247

30.7 Clock and Reset Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 247

30.8 UART Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 249

30.9 I/O Port Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 250

30.10 Advanced Audio Interface (AAI) Timing . . . . . . . . . . . . . . . . . . . 251

30.11 Microwire/SPI Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 253

30.12 ACCESS.bus Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 258

30.13 USB Port AC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . 261

30.14

30.15 Versatile Timing Unit (VTU) Timing . . . . . . . . . . . . . . . . . . . . . . 262

30.16 External Bus Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 263

31.0 Pin Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . 269

31.1

31.2

32.0 Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . 276 33.0 Physical Dimensions . . . . . . . . . . . . . . . . . . . . . . . . 277

www.national.com | 2 |