General Description

Block Diagram

MAY

National Semiconductor Corporation

Table of Contents

Features

Device Overview

Can Interface

Bluetooth LLC

Quad Uart

Advanced Audio Interface

ACCESS.BUS Interface

MICROWIRE/SPI

MULTI-FUNCTION Timer

Versatile Timer Unit

DMA Controller

Power Management

Serial Debug Interface

Development Support

CP3BT26

Signal Descriptions

LQFP-128

LQFP-144

X1CKI

Reset

Bbclk

X1CKO

Name Pins Primary Function Alternate Alternate Function

Sdat

PG4

PG5

PG6

X1CKI

WR0

Selio

WR1

CTS PE4

SLE

Dedicated Address Registers

CPU Architecture

GENERAL-PURPOSE Registers

Interrupt Base Register Intbase

Processor Status Register PSR

12 11 Reserved

No carry or borrow occurred Carry or borrow occurred

When the IDT has 16-bit entries, and all ex

Configuration Register CFG

Mode for the CR16B large model.

Is held in the Intbase register, which is not

Loadw 12R5, R6

Addressing Modes

Addb R1, R2

Instruction SET

Stacks

Instruction Set Summary Mnemonic Operands Description

Lshd

Ashud

Tbit

LPR

Push

Retx

POP

Popret

Eiwait

Stormp

NOP

Wait

IN/A

Memory

Operating Environment

BUS Cycles

BUS Interface Unit BIU

BIU Control Registers

Empty

Static Zone 0 Configuration Register SZCFG0

2 I/O Zone Configuration Register Iocfg

WBR RBE Hold Wait Ipst

Static Zone 1 Configuration Register SZCFG1

Static Zone 2 Configuration Register SZCFG2

Wait and Hold States

Access to Peripherals

Flash Program/Data Memory

RAM Memory

System Configuration Registers Name Address Description

System Configuration Registers

Module Configuration Register Mcfg

Module Status Register Mstat

Software Reset Register Swreset

Flash Memory Organization

Flash Memory

Flash Memory Protection

Flash Memory Operations

Main Block Module Erase

Main Block Page Erase

Information Block Module Erase

Main Block Write

Area

Boot

Information Block Words

Boot Area Start-Up Operation

CPU Reset Behavior

Flash Memory Interface Registers

Empty Ispe

Flash Memory 1 Write Enable Register FM1WER

Flash Memory 0 Write Enable Register FM0WER/FSM0WER

Flash Memory Information Block Data Register

FMIBDR/FSMIBDR

Fsmctrl

Flash Data Memory 0 Write Enable Register FSM0WER

Flash Memory Control Register Fmctrl

FMSTART/FSMSTART

Fsmstat

Fsmpsr

Flash Memory End Time Reload Register FMEND/FSMEND

Flash Memory Auto-Read Register 2 FMAR2/ FSMAR2

FMRCV/FSMRCV FSMAR1

Flash Memory Auto-Read Register 0 FMAR0/ FSMAR0

Channel Assignment

DMA Controller

Transfer Types

DMA Channel Assignment Peripheral Trans Register Action

Operation Modes

DMA Controller Register SET

Debug Mode

Software DMA Request

Device a Address Register ADRAn

Device a Address Counter Register ADCAn

Device B Address Counter Register ADCBn

Device B Address Register ADRBn

DMA Control Register DMACNTLn

Block Length Register BLTRn

VLD

DMA Status Register Dmastat

VLD Chac OVR

NON-MASKABLE Interrupts

Interrupts

Maskable Interrupts

Interrupt Controller Registers

Non-Maskable Interrupt Status Register Nmistat

Interrupt Vector Register Ivct

External NMI Trap Control and Status Register Exnmi

Interrupt Enable and Mask Register 2 IENAM2

Interrupt Enable and Mask Register 1 IENAM1

Interrupt Status Register 1 ISTAT1

Interrupt Status Register 2 ISTAT2

Nested Interrupts

Maskable Interrupt Sources

Maskable Interrupts Assignment IRQ Number Description

IRQ Number Description

Triple Clock and Reset Module

Triple Clock and Reset

Crystal Resonance Frequency

External Crystal Network

Type

Capacitor C1, C2 Capacitance

Slow Clock

Main Clock

PLL Clock

Min. Q factor

External Reset

POWER-ON Reset

Clock and Reset Registers

System Clock

MODE20

Active Mode

Power Management

Power Save Mode

Module Activity Summary Power Mode Clock

Halt Mode

Idle Mode Power Management Registers

Power Management Registers Name Address Description

Power Management Control Register Pmmcr

Hcch

DHC

Hccm

OHC

Active Mode to Power Save Mode

OHC OMC OLC

Entering Halt Mode

Entering Idle Mode

Software-Controlled Transition to Active Mode

Wake-Up Transition to Active Mode

Multi-Input Wake-Up

Multi-Input Wake-Up Module Block Diagram

Miwu Sources

MULTI-INPUT WAKE-UP Registers

Miwu Channel

Multi-Input Wake-Up Registers Name Address Description

Wake-Up 1 Interrupt Enable Register WK1IENA

Wake-Up Interrupt Enable Register WK0IENA

Wake-Up Enable Register WK0ENA

Wake-Up 1 Edge Detection Register WK1EDG

WK0ICTL1 WK0ICTL2

Wake-Up Interrupt Control Register

Wake-Up 1 Interrupt Control Register

WK1ICTL1 WK1ICTL2

Wake-Up Pending Clear Register WK0PCL

Wake-Up Pending Register WK0PND

Wake-Up 1 Pending Register WK1PND

Wake-Up 1 Pending Clear Register WK1PCL

Programming Procedures

Port Registers

Input/Output Ports

Address Description

Port Registers

Port Data Input Register PxDIN

Port Alternate Function Register PxALT

Port Data Output Register PxDOUT

Port Direction Register PxDIR

Port Alternate Function Select Register PxALTS

Port High Drive Strength Register PxHDRV

Alternate Function Select

Port Pin PxALTS =

OPEN-DRAIN Operation

RF Interface

Bluetooth Controller

X1CKI/BBCLK

Rfdata

Rfce

Serial Interface

Sclk

Sdat

Serial Interface Write Timing Read Operation

Write Operation

First part of read cycle driven by CP3BT26. Address is 0Ah

Bit, and register address for a read cycle. In the second

15.4 LMX5252 POWER-UP Sequence

15.3 LMX5251 POWER-UP Sequence

Bluetooth Sequencer RAM

Bluetooth Sleep Mode

Bluetooth Global Registers

Bluetooth Shared Data RAM

Data Path

16.0 12-Bit Analog to Digital Converter

Functional Description

ADC Clock Generation

Operation

ADC Voltage References

Pen-Down Detector

Touchscreen Interface

Touchscreen Driver Configuration

RX2

Measuring Pen Force

RY2

RYP

Freeze

ADC Operation in POWER-SAVING Modes

ADC Register SET

ADC Registers Name Address Description

Touchcfg ADC0/TSX+ ADC1/TSY+ ADC2/TSX ADC3/TSY

Muxcfg

Clkdiv

Prefcfg

Nrefcfg

ADC Start Conversion Register Adcstart

ADC Start Conversion Delay Register Adcscdly

ADC Conversion Control Register Adccntrl

Adcresult

ADC Result Register Adcreslt

Adcoflw

Sign

Random Number Generator RNG

RNG Module Block Diagram

Random Number Generator Register SET

Functional States

USB Controller

TX Fifo RX Fifo

Endpoint Operation

Transmit Endpoint Fifo Operation TXFIFO1, TXFIFO2, TXFIFO3

Bidirectional Control Endpoint FIFO0 Operation

USB Controller Registers Name Address Description

USB Controller Registers

Receive Endpoint Fifo Operation RXFIFO1, RXFIFO2, RXFIFO3

Main Control Register Mcntrl

NFS

Node Functional State Register Nfsr

USB Functional States

NFS

Alternate Event Register Altev

Main Event Register Maev

Main Mask Register Mamsk

Transmit Mask Register Txmsk

Alternate Mask Register Altmsk

Transmit Event Register Txev

NAK Mask Register Nakmsk

Receive Event Register Rxev NAK Event Register Nakev

Receive Mask Register Rxmsk

Fifo Warning Mask Register Fwmsk

Fifo Warning Event Register Fwev

Frame Number High Byte Register FNH

Dsrc

DMA Event Register Dmaev

DMA Mask Register Dmamsk

DMA Error Register Dmaerr

Mirror Register MIR

DMA Count Register Dmacnt

Transmit Status 0 Register TXS0

Transmit Command 0 Register TXC0

Endpoint Control 0 Register EPC0

Receive Status 0 Register RXS0

Receive Command 0 Register RXC0

Transmit Data 0 Register TXD0

Transmit Status Register n TXSn

Receive Data 0 Register RXD0

Endpoint Control Register n EPCn

Tfwl

Transmit Command Register n TXCn

Last

RFF

Receive Status Register n RXSn

Transmit Fifo Warning Limit

Tfwl

Bytes Remaining in Fifo

Transceiver Interface

Receive Command Register n RXCn Receive Data Register n RXD

Receive Fifo Warning Limit

Rfwl

Can Module

Basic can Concepts

Can Block Diagram

Can Frame Fields

Can Frame Types

Start of Frame SOF

Arbitration Field

Data Field

Data Length Code DLC

Cyclic Redundancy Check CRC

ACK Field

Cyclic Redundancy Check Field CRC

Remote Frame

Data Field

Error Frame Overload Frame

Error Frame

Form Error

Stuff Error

Bit CRC Error

Acknowledgment Error

Error Warning

Error Active

Error Passive

Error Counters

Can Bit Time

Bit Time Logic

Synchronization

Bit Timing

CKI

Message Transfer

Example 1 Acceptance of a Single Identifier

Acceptance Filtering

Two 32-bit masks are used to filter unwanted messages

From the can bus Gmask and BMASK. shows

120

Receive Structure

Receive Timing

Receive Procedure

Writing to Buffer Status Code During

Rxbusy

122

Buffer Read Routine Bufflock Enabled

Transmit Priority

Transmit Structure

Transmit Scheduling

PRI

Txpri

TX Buffer States

Interrupts

IRQ IST3 IST2 IST1 IST0

Time Stamp Counter

Memory Organization

CPU Access to can Registers/Memory

Message Buffer Organization

Message Buffer Map Address Register

Buffer Status/Control Register Cnstat

Can Controller Registers

Can Controller Registers Name Address Description

Buffer Status

Buffer Status Section of the Cnstat Register

ST3 DIR ST2 ST1 ST0 Busy

DLC

Data Length Coding

Storage of Standard Messages

Standard Frame with 8 Data Bytes Address Buffer Register

PRI SRR

Extended Messages with 8 Data Bytes Address Buffer Register

Cnstat DLC

Contents of these registers are ignored. If a remote

Frame is received, the contents of these registers will be

Storage of Remote Messages

Extended Remote Frame Address Buffer Register

Can Global Configuration Register Cgcr

When the Ignore Acknowledge bit is set,

Listen Only bit can be used to configure

When the Loopback bit is set, all messages

Dress, as shown in Figure

SJW

TSEG2

TSEG1

RTR IDE

Xrtr

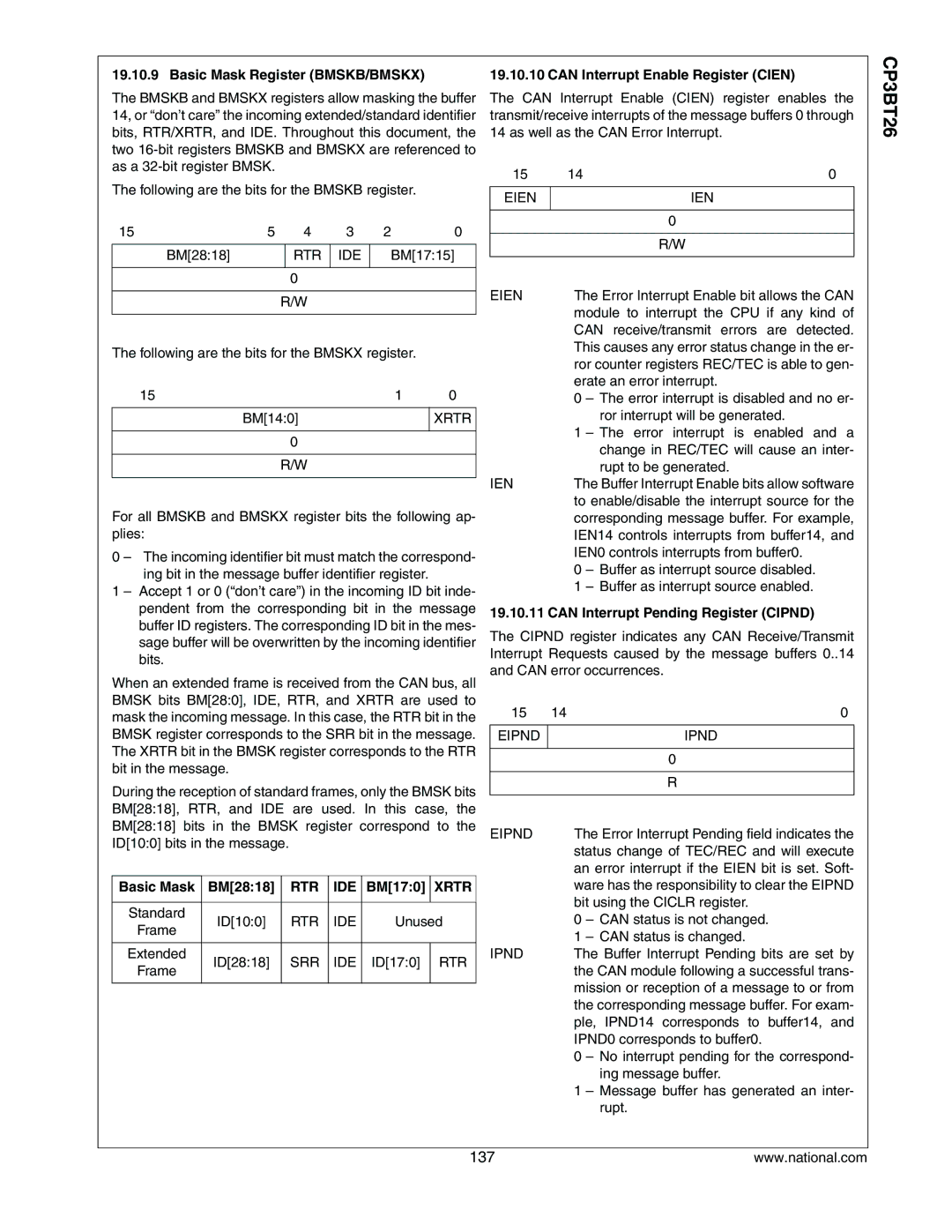

Basic Mask Register BMSKB/BMSKX

Can Interrupt Enable Register Cien

Basic Mask BM2818

BM170

IRQ

Can Error Diagnostic Register Cediag

Can Error Counter Register Canec

Error Field Identifier

EFID30

External can Pins Signal Name Type Description

Can Timer Register Ctmr

System START-UP and MULTI-INPUT WAKE-UP

External Connection

Bit Time Logic Calculation Examples

Minimum Clock Frequency Requirements Baud Rate

Acceptance Filter Considerations

Remote Frames

Usage Hint

Audio Interface Modes

Audio Interface Signals

Advanced Audio Interface

DMA Support

Synchronous Mode

Normal Mode

145

Frame Clock Generation

Clock Configuration

BIT Clock Generation

Audio Interface Operation

DMA Operation

Transmit

Fifo Operation

Receive

Data Word Length

Frame Sync Signal

Communication Options

Short and Long Frame Sync Pulses

Audio Control Data

150

IOM-2 Mode

Loopback Mode

Audio Interface Registers Name Address Description

Freeze Mode

Audio Interface Registers

Audio Transmit Fifo Register Atfr

Audio Receive Fifo Register Arfr

Audio Receive DMA Register n ARDRn

Audio Transmit DMA Register n ATDRn

Slots per Mode Frame

Audio Global Configuration Register Agcr

SCS

FSL

Txeip Txip Rxeip Rxip Txeie Txie Rxeie Rxie

Audio Interrupt Status and Control Register Aiscr

Txeic Txic Rxeic Rxic Rxie

Txeip

Audio Receive Status and Control Register Arscr

Rxsa Bit Slots Enabled

Rxdsa Bit Slots Enabled For DMA

Audio Transmit Status and Control Register Atscr

Txsa Bit Slots Enabled

Txdsa Bit Slots Enabled For DMA

Audio DMA Control Register Admacr

Audio Clock Control Register Accr

RMD

DMA Request Condition

PCM Conversions

CVSD/PCM Conversion Module

Operation

PCM to Cvsd Conversion

Cvsd Conversion

Cvsd to PCM Conversion

Interrupt Generation

CVSD/PCM Converter Registers

Linearout

Cvsd Status Register Cvstat

Uart Operation

Uart Modules

Functional Overview

Uart Asynchronous Communication

Uart Block Diagram

Frame Format Selection

Diagnostic Mode

Prescaler Factor

Prescaler Factors

Parity Generation and Detection

Break Generation and Detection

Uart Registers Name Address Description

Uart Registers

Uart Receive Data Buffer UnRBUF

Uart Baud Rate Divisor UnBAUD

Uart Transmit Data Buffer UnTBUF

Uart Frame Select Register UnFRS

Uart Status Register UnSTAT

Uart Mode Select Register 1 UnMDSL1

Uart Oversample Rate Register UnOVR

Uart Interrupt Control Register UnICTRL

UOVSR30

Oversampling Rate

Baud Rate Calculations

Uart Mode Select Register 2 UnMDSL2

Uart Sample Position Register UnSPOS

Oversampling Rate Sample Position

173

174

Microwire Operation

Microwire/SPI Interface

Microwire Interface

Shifting

Clocking Modes

Writing

Normal Mode Scidl =

Master Mode

MWCTRL1

Slave Mode

Microwire Interrupt Trigger Condition Status Enable Bit

Mwen

Microwire Interface Registers

SCM

Microwire Status Register Mwstat

Scdv

OVR RBF BSY

ACB Protocol Overview

ACCESS.bus Interface

Data Transactions

Start and Stop

Arbitration on the Bus

Acknowledge Cycle

Addressing Transfer Formats

ACB Functional Description

Bus Idle Error Recovery

Master Error Detections

Slave Mode

Slave Error Detections

ACCESS.BUS Interface Registers

ACB Control Status Register Acbcst

ACB Control Register 1 ACBCTL1

Tgscl

Start

Stop

ACB Control Register 3 ACBCTL3

ACB Control Register 2 ACBCTL2

ACB Own Address Register 1 ACBADDR1

Usage Hints

Saen Addr

Saen

190

Avoiding Bus Error During Write Transaction

191

TWM Structure

Timer T0 Operation

Timing and Watchdog Module

Watchdog Operation

Power Save Mode Operation

TWM Registers

Register Locking

T0IN

Mdiv

Watchdog Service Data Match Register Wdsdm

Watchdog Programming Procedure

TWMT0 Control and Status Register T0CSR

Watchdog Count Register Wdcnt

Timer Structure

Multi-Function Timer

Clock Source Block

196

Pulse Accumulate Mode

Timer Operating Modes

Limitations in Low-Power Modes

Counter Clock Source Select

198

Mode 1 Processor-Independent PWM

Dual-Input Capture Mode

Mode 2 Dual Input Capture

200

Mode 3 Dual Independent Timer/Counter

Input Capture Plus Timer Mode

Mode 4 Input Capture Plus Timer

Timer I/O Functions

Timer Interrupts

Taen

Tben

Timer Registers

Reload/Capture B Register Tcrb

Timer Mode Control Register Tctrl

Reload/Capture a Register Tcra

Timer Interrupt Clear Register Ticlr

Timer Interrupt Control Register Tictl

206

Versatile Timer Unit VTU

VTU Functional Description

VTU PWM Generation

Dual 8-bit PWM Mode

208

VTU 16-bit PWM Mode Dual 16-Bit Capture Mode

ISE Mode operation

VTU Dual 16-bit Capture Mode Low Power Mode

VTU Registers Name Address Description

Mode Control Register Mode

VTU Registers

Interrupt Control Register Intctl

CxEDG Capture Counter Reset

Clock Prescaler Register 2 CLK2PS

Clock Prescaler Register 1 CLK1PS

Interrupt Pending Register Intpnd

CNTx

Counter Register n COUNTx

Duty Cycle/Capture Register n DTYCAPx

Period/Capture Register n PERCAPx

Register Map

Bluetooth LLC Registers

USB Node Registers

Register Name Size Address Access Value After Comments Type

TXC1

EPC1

EPC2

EPC4

Can Module Message Buffers

DMA Controller

Can Registers

Bus Interface Unit

Flash Data Memory Interface

System Configuration

Flash Program Memory Interface

CVSD/PCM Converter

Triple Clock + Reset

General-Purpose I/O Ports

Multi-Input Wake-Up

Comments Type

Register Name Size Address

Interrupt Control Unit

Advanced Audio Interface

UART1

UART0

UART3

UART2

Timing and Watchdog

ACCESS.bus

Multi-Function Timer

ADC

Versatile Timer Unit

Rngcst

RNG

Rngd

Word FF F284h

Register Bit Fields

USB

IGN Ignout Rxen Setup EPC1

Setup Toggle Rxlast Rcount RXC0

Nakev OUT Nakmsk Fwev RXWARN31

Fwmsk RXWARN31

Control Status

Can

Dmac

Memory Registers

BIU

System Configuration Registers

TBI Register

Flash

Flash Data Memory

CLK3RES

CVSD/PCM

MIWU16

PMM Register

Gpio Registers

AAI

Uart

ICU Registers

MFT16

MWSPI16

ACB Registers

VTU

Imsk

Rngcst

Rngd

Rngdivh

Symbol Parameter Conditions Min Max Units

Electrical Characteristics

Absolute Maximum Ratings

TBD

IOOff

INL

Symbol Parameter Conditions Min Typ Max Units

LSB

DNL

Flash Memory ON-CHIP Programming

Clock and Reset Timing

Output Signal Levels

Reset and NMI Input Signals

TRI-STATE

Clock Timing

NMI Signal Timing

Uart Timing

Uart Output Signals

30.9 I/O Port Timing

Port Output Signals

Advanced Audio Interface AAI Timing

AAI Output Signals

Receive Timing, Long Frame Sync

Transmit Timing, Short Frame Sync

Microwire/SPI Signals Symbol Description Reference Min ns

MICROWIRE/SPI Timing

Microwire/SPI Input Signals

Microwire/SPI Output Signals

Microwire Data Out Valid

Normal Mode After FE on

Alternate Mode After RE On MSK Propagation Time

254

255

256

Microwire Transaction Timing, Alternate Mode, Scidl =

257

ACCESS.bus Output Signals

ACCESS.BUS Timing

259

260

ACB Data Timing

MULTI-FUNCTION Timer MFT Timing

USB Port AC Characteristics

TIOx Input High Time Rising Edge RE on CLK

Versatile Timing Unit VTU Timing

TIOx Input Low Time RE on CLK

262

External BUS Timing

External Bus Output Signals

264

Early Write Between Normal Read Cycles No Wait States

265

266

Consecutive Normal Read Cycles Burst, No Wait States

267

268

Early Write Between Fast Read Cycles

LQFP-128 Package

Pin Assignments

PWR

X1CKO X1CKI

Avcc PWR Adgnd Advcc Uvcc

Reset TMS

X2CKI X2CKO ENV2

SDA ADC0 TSX+

SRFS/NMI

PE0 RXD0 Gpio PE1 TXD0 PE2 RTS PE3 CTS PE4 CKX/TB PE5

PF0 MSK/TIO1

PF1 MDIDO/TIO2

272

LQFP-144 Package

ADC4 MUXOUT0

SCL SDA ADC0 TSX+

ADC5 MUXOUT1

ADC7 Adcin

Pin Name Alternate Functions Pin Number Type

A12

A22 A21 A20 A19 A18 A17 A16 A15 A14 A13

A11

A10

Date Major Changes From Previous Version

Revision History

Revision History

LQFP-128 Package LQFP-144 Package

Physical Dimensions millimeters unless otherwise noted

Banned Substance Compliance

Form when properly used in accordance with instructions

Life Support Policy