Memory concept 4.1 Memory areas and retentivity

Retentive data in RAM

Therefore, the contents of retentive DBs are always retentive at restart and POWER ON/OFF.

CPUs V2.1.0 or higher also support volatile DBs (the volatile DBs are initialized at restart of POWER

See also

Properties of the Micro Memory Card (MMC) (Page

4.1.3Retentivity of memory objects

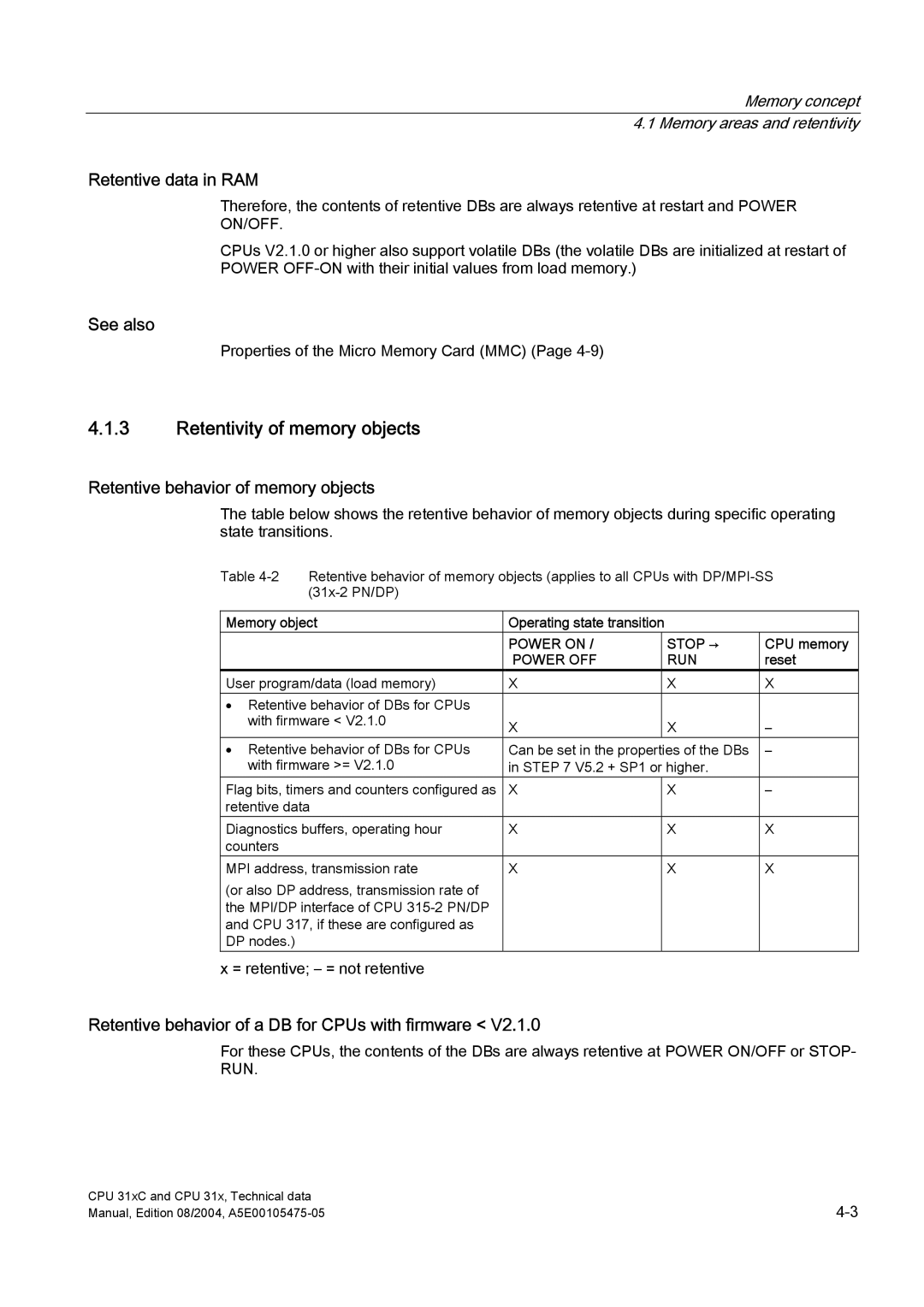

Retentive behavior of memory objects

The table below shows the retentive behavior of memory objects during specific operating state transitions.

Table | Retentive behavior of memory objects (applies to all CPUs with | ||||

|

|

|

|

| |

|

|

|

|

| |

Memory object | Operating state transition |

|

| ||

|

| POWER ON / |

| STOP → | CPU memory |

|

| POWER OFF |

| RUN | reset |

User program/data (load memory) | X |

| X | X | |

• Retentive behavior of DBs for CPUs |

|

|

|

| |

with firmware < V2.1.0 | X |

| X | – | |

|

|

| |||

• Retentive behavior of DBs for CPUs | Can be set in the properties of the DBs | – | |||

with firmware >= V2.1.0 | in STEP 7 V5.2 + SP1 or higher. |

| |||

Flag bits, timers and counters configured as | X |

| X | – | |

retentive data |

|

|

|

| |

Diagnostics buffers, operating hour | X |

| X | X | |

counters |

|

|

|

|

|

MPI address, transmission rate | X |

| X | X | |

(or also DP address, transmission rate of |

|

|

|

| |

the MPI/DP interface of CPU |

|

|

|

| |

and CPU 317, if these are configured as |

|

|

|

| |

DP nodes.) |

|

|

|

|

|

x = retentive; – = not retentive

Retentive behavior of a DB for CPUs with firmware < V2.1.0

For these CPUs, the contents of the DBs are always retentive at POWER ON/OFF or STOP- RUN.

CPU 31xC and CPU 31x, Technical data | |

Manual, Edition 08/2004, |