Status Registers

Overview

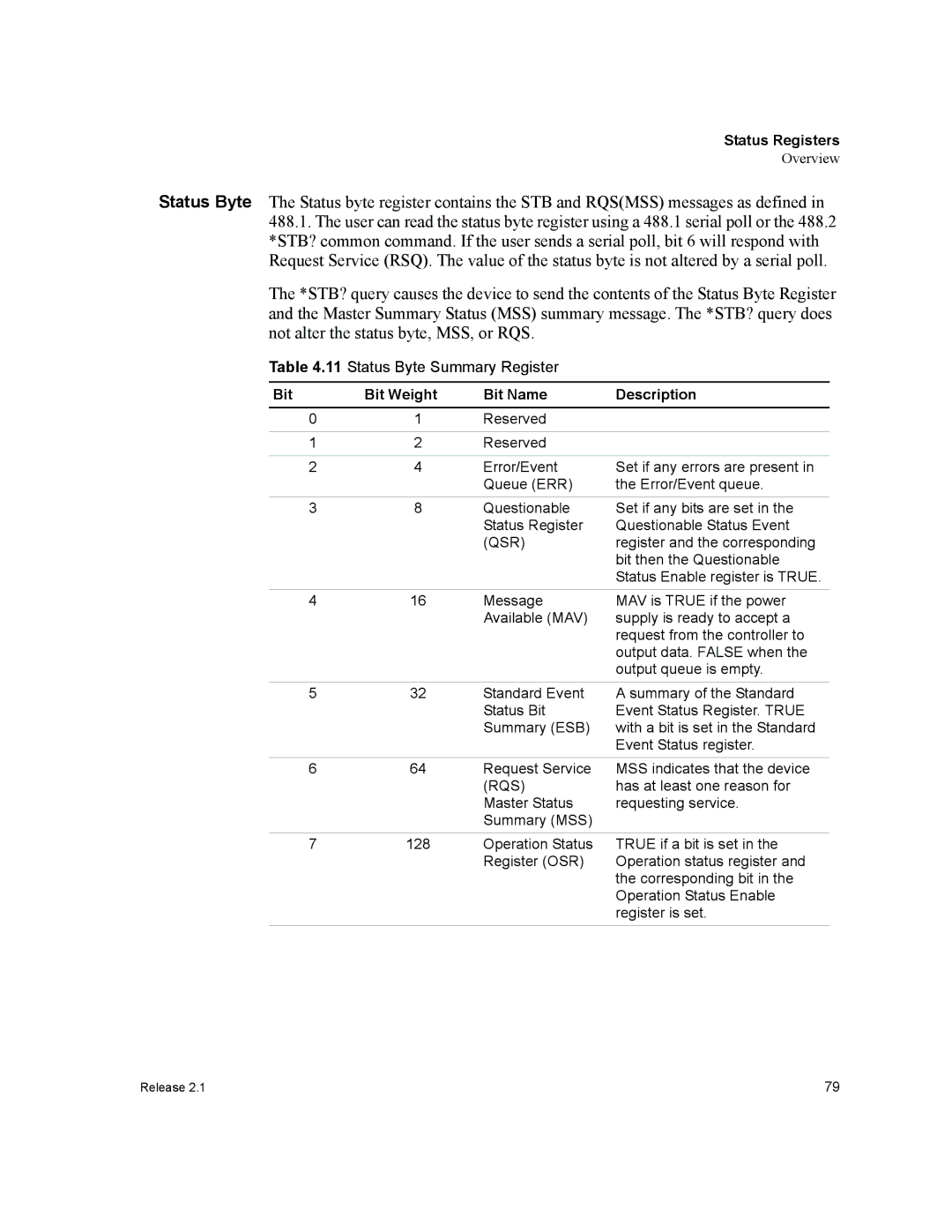

Status Byte The Status byte register contains the STB and RQS(MSS) messages as defined in

488.1.The user can read the status byte register using a 488.1 serial poll or the 488.2 *STB? common command. If the user sends a serial poll, bit 6 will respond with Request Service (RSQ). The value of the status byte is not altered by a serial poll.

The *STB? query causes the device to send the contents of the Status Byte Register and the Master Summary Status (MSS) summary message. The *STB? query does not alter the status byte, MSS, or RQS.

Table 4.11 Status Byte Summary Register

Bit | Bit Weight | Bit Name | Description |

0 | 1 | Reserved |

|

|

|

|

|

1 | 2 | Reserved |

|

|

|

|

|

2 | 4 | Error/Event | Set if any errors are present in |

|

| Queue (ERR) | the Error/Event queue. |

|

|

|

|

3 | 8 | Questionable | Set if any bits are set in the |

|

| Status Register | Questionable Status Event |

|

| (QSR) | register and the corresponding |

|

|

| bit then the Questionable |

|

|

| Status Enable register is TRUE. |

4 | 16 | Message | MAV is TRUE if the power |

|

| Available (MAV) | supply is ready to accept a |

|

|

| request from the controller to |

|

|

| output data. FALSE when the |

|

|

| output queue is empty. |

5 | 32 | Standard Event | A summary of the Standard |

|

| Status Bit | Event Status Register. TRUE |

|

| Summary (ESB) | with a bit is set in the Standard |

|

|

| Event Status register. |

6 | 64 | Request Service | MSS indicates that the device |

|

| (RQS) | has at least one reason for |

|

| Master Status | requesting service. |

|

| Summary (MSS) |

|

|

|

|

|

7 | 128 | Operation Status | TRUE if a bit is set in the |

|

| Register (OSR) | Operation status register and |

|

|

| the corresponding bit in the |

|

|

| Operation Status Enable |

|

|

| register is set. |

Release 2.1 | 79 |