—For package

—Entry into a package

The processor exits a package

•If a core break event is received, the target core is activated and the break event message is forwarded to the target core.

—If the break event is not masked, the target core enters the core C0 state and the processor enters package C0 state.

—If the break event is masked, the processor attempts to

•If the break event was due to a memory access or snoop request,

—But the platform did not request to keep the processor in a higher package C- state, the package returns to its previous

—And the platform requests a higher power

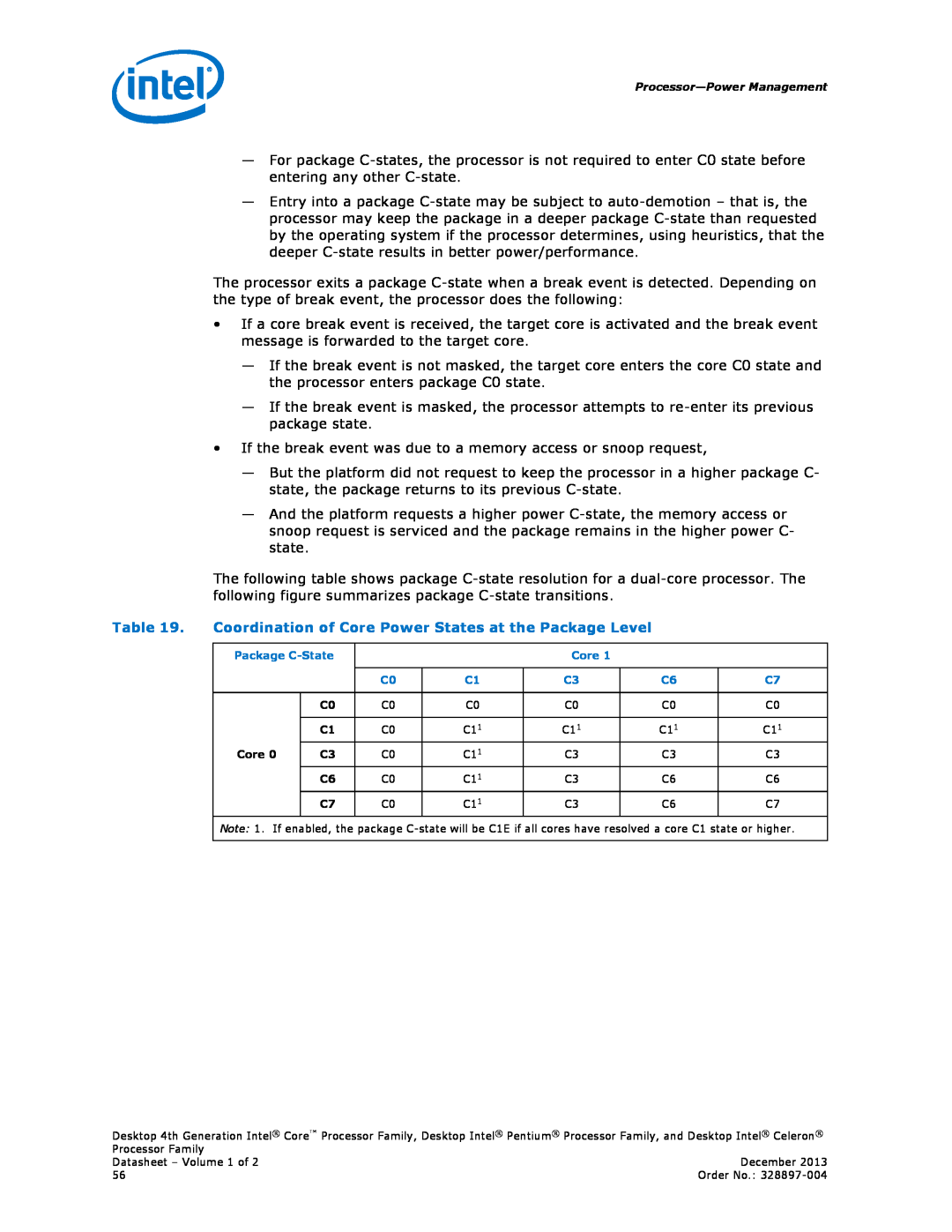

The following table shows package

Table 19. | Coordination of Core Power States at the Package Level |

|

| |||||

|

|

|

|

|

|

|

|

|

| Package |

|

| Core 1 |

|

| ||

|

|

|

|

|

|

|

|

|

|

|

| C0 | C1 | C3 |

| C6 | C7 |

|

|

|

|

|

|

|

|

|

|

| C0 | C0 | C0 | C0 |

| C0 | C0 |

|

|

|

|

|

|

|

|

|

|

| C1 | C0 | C11 | C11 |

| C11 | C11 |

| Core 0 | C3 | C0 | C11 | C3 |

| C3 | C3 |

|

| C6 | C0 | C11 | C3 |

| C6 | C6 |

|

| C7 | C0 | C11 | C3 |

| C6 | C7 |

Note: 1. If enabled, the package

Desktop 4th Generation Intel® Core™ Processor Family, Desktop Intel® Pentium® Processor Family, and Desktop Intel® Celeron® Processor Family

Datasheet – Volume 1 of 2 56