Hardware Design

3.6.1Signal Interface

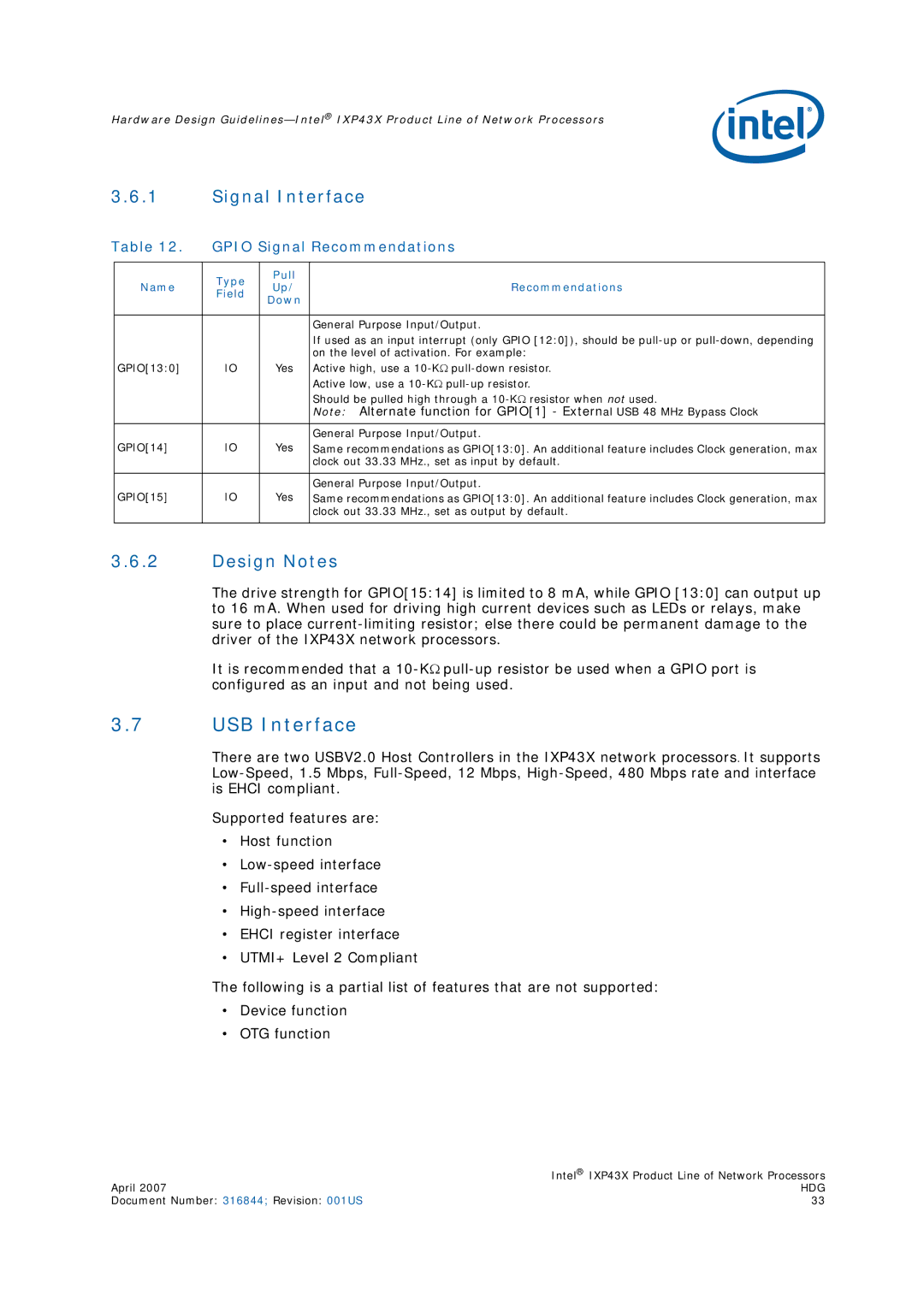

Table 12. | GPIO Signal Recommendations | |||

|

|

|

|

|

|

| Type | Pull |

|

| Name | Up/ | Recommendations | |

| Field | |||

|

| Down |

| |

|

|

|

| |

|

|

|

|

|

|

|

|

| General Purpose Input/Output. |

|

|

|

| If used as an input interrupt (only GPIO [12:0]), should be |

|

|

|

| on the level of activation. For example: |

| GPIO[13:0] | IO | Yes | Active high, use a |

|

|

|

| Active low, use a |

|

|

|

| Should be pulled high through a |

|

|

|

| Note: Alternate function for GPIO[1] - External USB 48 MHz Bypass Clock |

|

|

|

|

|

|

|

|

| General Purpose Input/Output. |

| GPIO[14] | IO | Yes | Same recommendations as GPIO[13:0]. An additional feature includes Clock generation, max |

|

|

|

| clock out 33.33 MHz., set as input by default. |

|

|

|

|

|

|

|

|

| General Purpose Input/Output. |

| GPIO[15] | IO | Yes | Same recommendations as GPIO[13:0]. An additional feature includes Clock generation, max |

|

|

|

| clock out 33.33 MHz., set as output by default. |

|

|

|

|

|

3.6.2Design Notes

The drive strength for GPIO[15:14] is limited to 8 mA, while GPIO [13:0] can output up to 16 mA. When used for driving high current devices such as LEDs or relays, make sure to place

It is recommended that a

3.7USB Interface

There are two USBV2.0 Host Controllers in the IXP43X network processors. It supports

Supported features are:

•Host function

•

•

•

•EHCI register interface

•UTMI+ Level 2 Compliant

The following is a partial list of features that are not supported:

•Device function

•OTG function

| Intel® IXP43X Product Line of Network Processors |

April 2007 | HDG |

Document Number: 316844; Revision: 001US | 33 |