Hardware Design

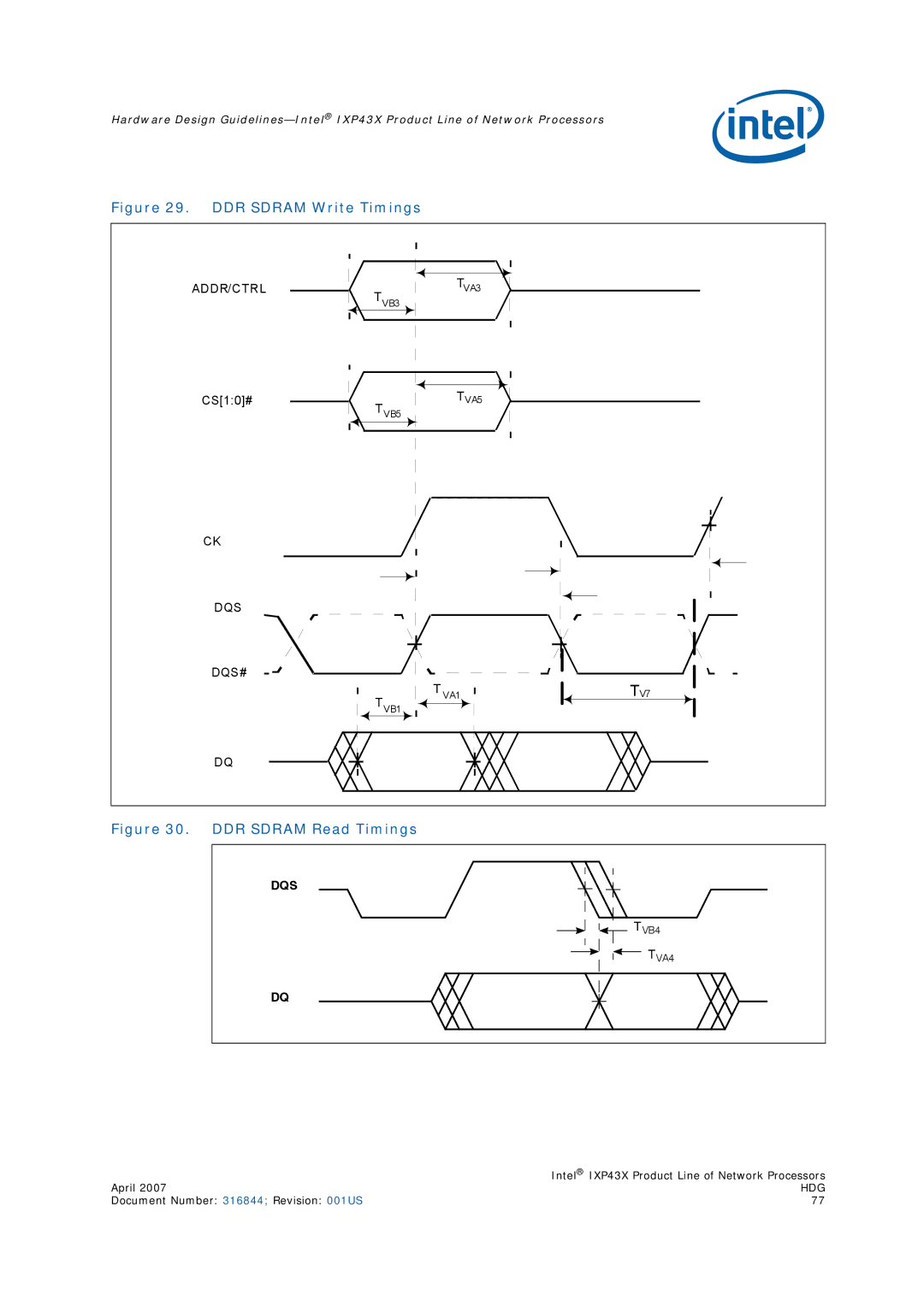

Figure 29. DDR SDRAM Write Timings

ADDR/CTRL

TVB3

TVA3

CS[1:0]#

CK

DQS

DQS #

DQ

TVA5

TVB5

|

|

|

| TVB1 |

| T VA1 |

|

| TV7 | ||||||

|

|

|

|

| |||||||||||

|

|

|

|

| |||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Figure 30. DDR SDRAM Read Timings

DQS

TVB4

TVA4

DQ

| Intel® IXP43X Product Line of Network Processors |

April 2007 | HDG |

Document Number: 316844; Revision: 001US | 77 |