Hardware Design

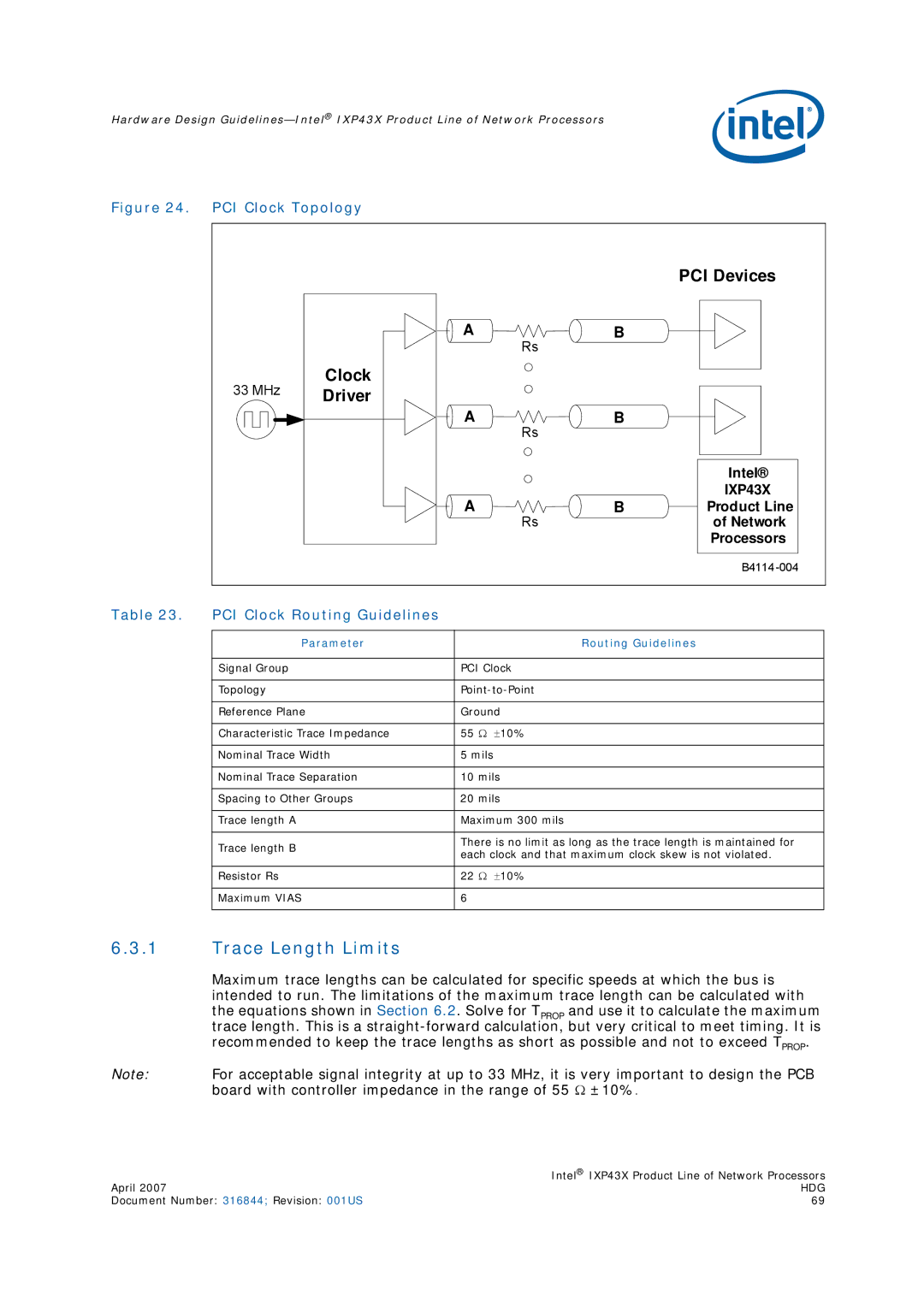

Figure 24. PCI Clock Topology

|

|

| PCI Devices |

| A | B |

|

| Rs |

|

|

33 MHz | Clock |

|

|

Driver |

|

| |

| A | B |

|

| Rs |

|

|

|

|

| Intel® |

| A | B | IXP43X |

| Product Line | ||

| Rs |

| of Network |

|

|

| Processors |

|

|

| B4114 |

Table 23. | PCI Clock Routing Guidelines |

|

|

|

|

| Parameter | Routing Guidelines |

|

|

|

| Signal Group | PCI Clock |

|

|

|

| Topology | |

|

|

|

| Reference Plane | Ground |

|

|

|

| Characteristic Trace Impedance | 55 Ω ±10% |

|

|

|

| Nominal Trace Width | 5 mils |

|

|

|

| Nominal Trace Separation | 10 mils |

|

|

|

| Spacing to Other Groups | 20 mils |

|

|

|

| Trace length A | Maximum 300 mils |

|

|

|

| Trace length B | There is no limit as long as the trace length is maintained for |

| each clock and that maximum clock skew is not violated. | |

|

| |

|

|

|

| Resistor Rs | 22 Ω ±10% |

|

|

|

| Maximum VIAS | 6 |

|

|

|

6.3.1Trace Length Limits

Maximum trace lengths can be calculated for specific speeds at which the bus is intended to run. The limitations of the maximum trace length can be calculated with the equations shown in Section 6.2. Solve for TPROP and use it to calculate the maximum trace length. This is a

Note: For acceptable signal integrity at up to 33 MHz, it is very important to design the PCB board with controller impedance in the range of 55 Ω ±10%.

| Intel® IXP43X Product Line of Network Processors |

April 2007 | HDG |

Document Number: 316844; Revision: 001US | 69 |