Intel® IXP43X Product Line of Network

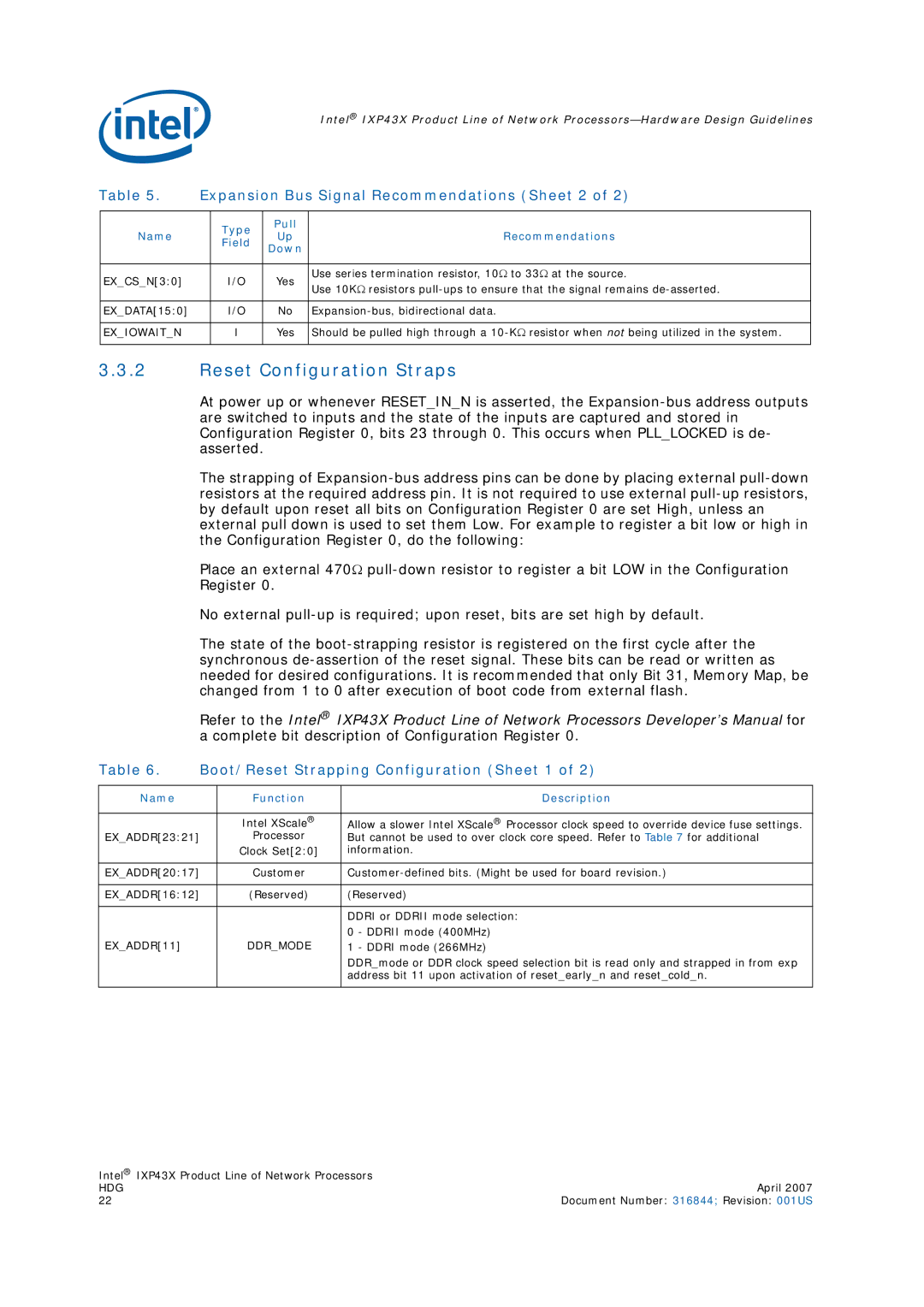

Table 5. | Expansion Bus Signal Recommendations (Sheet 2 of 2) | |||

|

|

|

|

|

Name |

| Type | Pull |

|

| Up | Recommendations | ||

| Field | |||

|

| Down |

| |

|

|

|

| |

|

|

|

|

|

EX_CS_N[3:0] |

| I/O | Yes | Use series termination resistor, 10Ω to 33Ω at the source. |

| Use 10KΩ resistors | |||

|

|

|

| |

|

|

|

|

|

EX_DATA[15:0] |

| I/O | No | |

|

|

|

|

|

EX_IOWAIT_N |

| I | Yes | Should be pulled high through a |

|

|

|

|

|

3.3.2Reset Configuration Straps

At power up or whenever RESET_IN_N is asserted, the

The strapping of

Place an external 470Ω

No external

The state of the

Refer to the Intel® IXP43X Product Line of Network Processors Developer’s Manual for a complete bit description of Configuration Register 0.

Table 6. | Boot/Reset Strapping Configuration (Sheet 1 of 2) | ||

|

|

|

|

Name |

| Function | Description |

|

|

|

|

|

| Intel XScale® | Allow a slower Intel XScale® Processor clock speed to override device fuse settings. |

EX_ADDR[23:21] | Processor | But cannot be used to over clock core speed. Refer to Table 7 for additional | |

|

| Clock Set[2:0] | information. |

|

|

| |

EX_ADDR[20:17] | Customer | ||

|

|

| |

EX_ADDR[16:12] | (Reserved) | (Reserved) | |

|

|

|

|

|

|

| DDRI or DDRII mode selection: |

|

|

| 0 - DDRII mode (400MHz) |

EX_ADDR[11] |

| DDR_MODE | 1 - DDRI mode (266MHz) |

|

|

| DDR_mode or DDR clock speed selection bit is read only and strapped in from exp |

|

|

| address bit 11 upon activation of reset_early_n and reset_cold_n. |

|

|

|

|

Intel® IXP43X Product Line of Network Processors |

|

HDG | April 2007 |

22 | Document Number: 316844; Revision: 001US |