Intel® IXP43X Product Line of Network

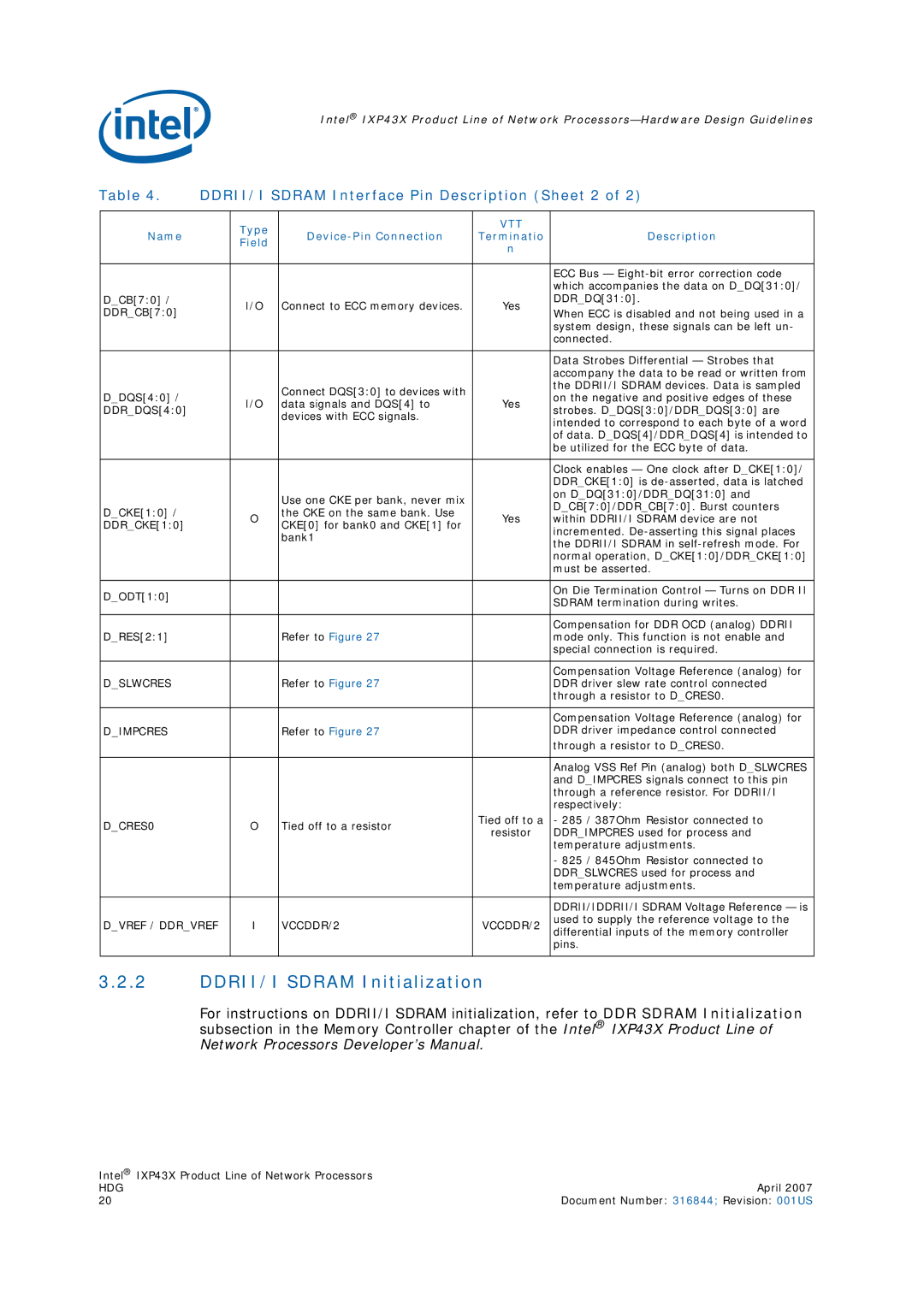

Table 4. | DDRII/I SDRAM Interface Pin Description (Sheet 2 of 2) | ||||

|

|

|

|

|

|

|

| Type |

| VTT |

|

Name |

| Terminatio | Description | ||

| Field | ||||

|

|

| n |

| |

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

| ECC Bus — |

|

|

|

|

| which accompanies the data on D_DQ[31:0]/ |

D_CB[7:0] / |

| I/O | Connect to ECC memory devices. | Yes | DDR_DQ[31:0]. |

DDR_CB[7:0] |

| When ECC is disabled and not being used in a | |||

|

|

|

| ||

|

|

|

|

| system design, these signals can be left un- |

|

|

|

|

| connected. |

|

|

|

|

|

|

|

|

|

|

| Data Strobes Differential — Strobes that |

|

|

|

|

| accompany the data to be read or written from |

|

|

| Connect DQS[3:0] to devices with |

| the DDRII/I SDRAM devices. Data is sampled |

D_DQS[4:0] / |

|

|

| on the negative and positive edges of these | |

| I/O | data signals and DQS[4] to | Yes | ||

DDR_DQS[4:0] |

| strobes. D_DQS[3:0]/DDR_DQS[3:0] are | |||

|

| devices with ECC signals. |

| ||

|

|

|

| intended to correspond to each byte of a word | |

|

|

|

|

| |

|

|

|

|

| of data. D_DQS[4]/DDR_DQS[4] is intended to |

|

|

|

|

| be utilized for the ECC byte of data. |

|

|

|

|

|

|

|

|

|

|

| Clock enables — One clock after D_CKE[1:0]/ |

|

|

|

|

| DDR_CKE[1:0] is |

|

|

| Use one CKE per bank, never mix |

| on D_DQ[31:0]/DDR_DQ[31:0] and |

D_CKE[1:0] / |

|

|

| D_CB[7:0]/DDR_CB[7:0]. Burst counters | |

| O | the CKE on the same bank. Use | Yes | ||

| within DDRII/I SDRAM device are not | ||||

DDR_CKE[1:0] |

| CKE[0] for bank0 and CKE[1] for | |||

|

|

| incremented. | ||

|

|

| bank1 |

| |

|

|

|

| the DDRII/I SDRAM in | |

|

|

|

|

| |

|

|

|

|

| normal operation, D_CKE[1:0]/DDR_CKE[1:0] |

|

|

|

|

| must be asserted. |

|

|

|

|

|

|

D_ODT[1:0] |

|

|

|

| On Die Termination Control — Turns on DDR II |

|

|

|

| SDRAM termination during writes. | |

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

| Compensation for DDR OCD (analog) DDRII |

D_RES[2:1] |

|

| Refer to Figure 27 |

| mode only. This function is not enable and |

|

|

|

|

| special connection is required. |

|

|

|

|

|

|

|

|

|

|

| Compensation Voltage Reference (analog) for |

D_SLWCRES |

|

| Refer to Figure 27 |

| DDR driver slew rate control connected |

|

|

|

|

| through a resistor to D_CRES0. |

|

|

|

|

|

|

|

|

|

|

| Compensation Voltage Reference (analog) for |

D_IMPCRES |

|

| Refer to Figure 27 |

| DDR driver impedance control connected |

|

|

|

|

| through a resistor to D_CRES0. |

|

|

|

|

|

|

|

|

|

|

| Analog VSS Ref Pin (analog) both D_SLWCRES |

|

|

|

|

| and D_IMPCRES signals connect to this pin |

|

|

|

|

| through a reference resistor. For DDRII/I |

|

|

|

|

| respectively: |

D_CRES0 |

| O | Tied off to a resistor | Tied off to a | - 285 / 387Ohm Resistor connected to |

| resistor | DDR_IMPCRES used for process and | |||

|

|

|

| ||

|

|

|

|

| temperature adjustments. |

|

|

|

|

| - 825 / 845Ohm Resistor connected to |

|

|

|

|

| DDR_SLWCRES used for process and |

|

|

|

|

| temperature adjustments. |

|

|

|

|

|

|

|

|

|

|

| DDRII/IDDRII/I SDRAM Voltage Reference — is |

D_VREF / DDR_VREF | I | VCCDDR/2 | VCCDDR/2 | used to supply the reference voltage to the | |

differential inputs of the memory controller | |||||

|

|

|

|

| pins. |

|

|

|

|

|

|

3.2.2DDRII/I SDRAM Initialization

For instructions on DDRII/I SDRAM initialization, refer to DDR SDRAM Initialization subsection in the Memory Controller chapter of the Intel® IXP43X Product Line of Network Processors Developer’s Manual.

Intel® IXP43X Product Line of Network Processors |

|

HDG | April 2007 |

20 | Document Number: 316844; Revision: 001US |