Intel® IXP43X Product Line of Network

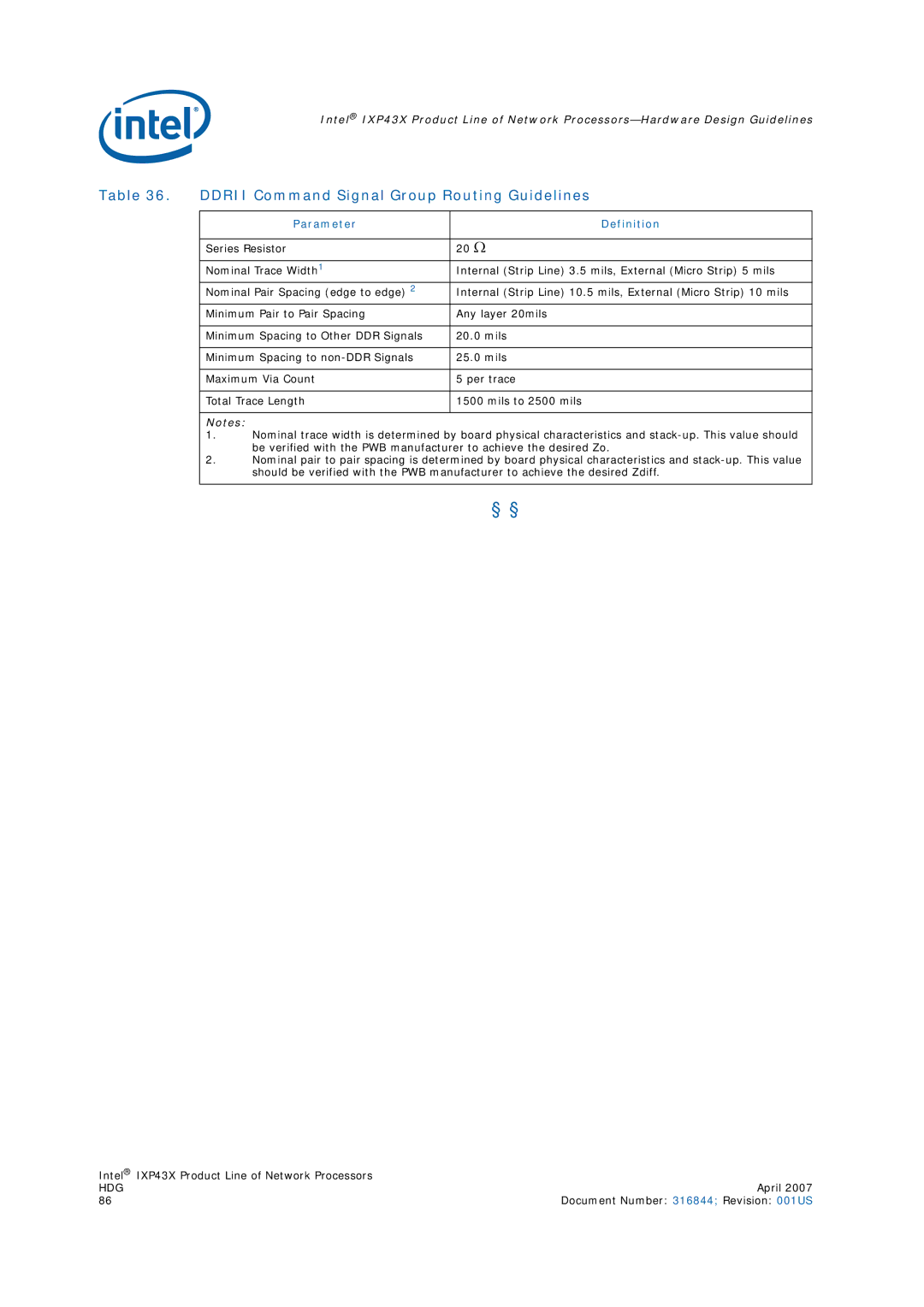

Table 36. DDRII Command Signal Group Routing Guidelines

Parameter | Definition |

|

|

Series Resistor | 20 Ω |

|

|

Nominal Trace Width1 | Internal (Strip Line) 3.5 mils, External (Micro Strip) 5 mils |

Nominal Pair Spacing (edge to edge) 2 | Internal (Strip Line) 10.5 mils, External (Micro Strip) 10 mils |

Minimum Pair to Pair Spacing | Any layer 20mils |

|

|

Minimum Spacing to Other DDR Signals | 20.0 mils |

|

|

Minimum Spacing to | 25.0 mils |

|

|

Maximum Via Count | 5 per trace |

|

|

Total Trace Length | 1500 mils to 2500 mils |

|

|

Notes:

1. Nominal trace width is determined by board physical characteristics and

2. Nominal pair to pair spacing is determined by board physical characteristics and

§ §

Intel® IXP43X Product Line of Network Processors |

|

HDG | April 2007 |

86 | Document Number: 316844; Revision: 001US |