Hardware Design

3.3Expansion Bus

The Expansion Bus of the IXP43X network processors is specifically designed for compatibility with

The expansion bus controller includes a

• | Intel multiplexed | • | Intel |

• | Intel StrataFlash® | • | Synchronous Intel StrataFlash® Memory |

• | Motorola non multiplexed | • | Motorola multiplexed |

The expansion bus controller also has an arbiter that supports up to four external devices that can master the expansion bus. External masters can be used to access external slave devices that reside on the expansion bus, including access to internal memory mapped regions within the IXP43X network processors.

All supported modes are seamless and no additional glue logic is required. Other cycle types can be supported by configuring the Timing and Control Register for Chip Select.

The expansion interface functions support

Access to the

The expansion interface is an asynchronous interface to externally connected chips. A clock is supplied to the IXP43X network processors expansion interface for the interface to operate. This clock can be driven from GPIO 15 or an external source. Devices on the expansion bus can be clocked by an external clock at a rate of up to 80 MHz. If GPIO 15 is used as the clock source, the Expansion Bus interface can only be clocked at a maximum of 33.33 MHz. GPIO 15’s maximum clock rate is 33.33 MHz.

3.3.1Signal Interface

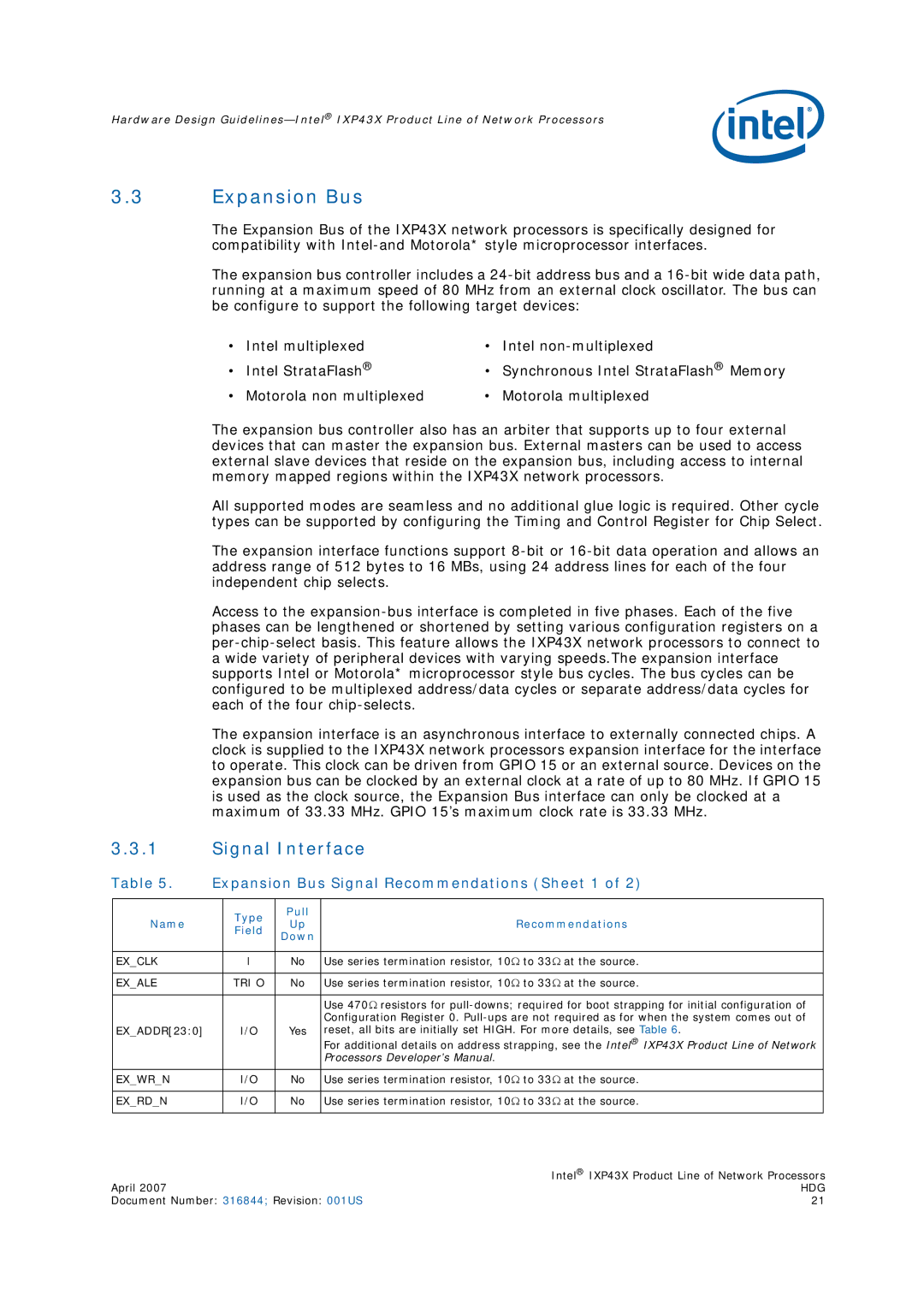

Table 5. | Expansion Bus Signal Recommendations (Sheet 1 of 2) | |||

|

|

|

|

|

|

| Type | Pull |

|

Name |

| Up | Recommendations | |

| Field | |||

|

| Down |

| |

|

|

|

| |

|

|

|

|

|

EX_CLK |

| I | No | Use series termination resistor, 10Ω to 33Ω at the source. |

|

|

|

|

|

EX_ALE |

| TRI O | No | Use series termination resistor, 10Ω to 33Ω at the source. |

|

|

|

|

|

|

|

|

| Use 470Ω resistors for |

|

|

|

| Configuration Register 0. |

EX_ADDR[23:0] |

| I/O | Yes | reset, all bits are initially set HIGH. For more details, see Table 6. |

|

|

|

| For additional details on address strapping, see the Intel® IXP43X Product Line of Network |

|

|

|

| Processors Developer’s Manual. |

|

|

|

|

|

EX_WR_N |

| I/O | No | Use series termination resistor, 10Ω to 33Ω at the source. |

|

|

|

|

|

EX_RD_N |

| I/O | No | Use series termination resistor, 10Ω to 33Ω at the source. |

|

|

|

|

|

| Intel® IXP43X Product Line of Network Processors |

April 2007 | HDG |

Document Number: 316844; Revision: 001US | 21 |