Hardware Design

|

| Type | Pull |

| |

| Name | Up/ | Description | ||

| Field | ||||

|

| Down |

| ||

|

|

|

| ||

|

|

|

|

| |

|

|

|

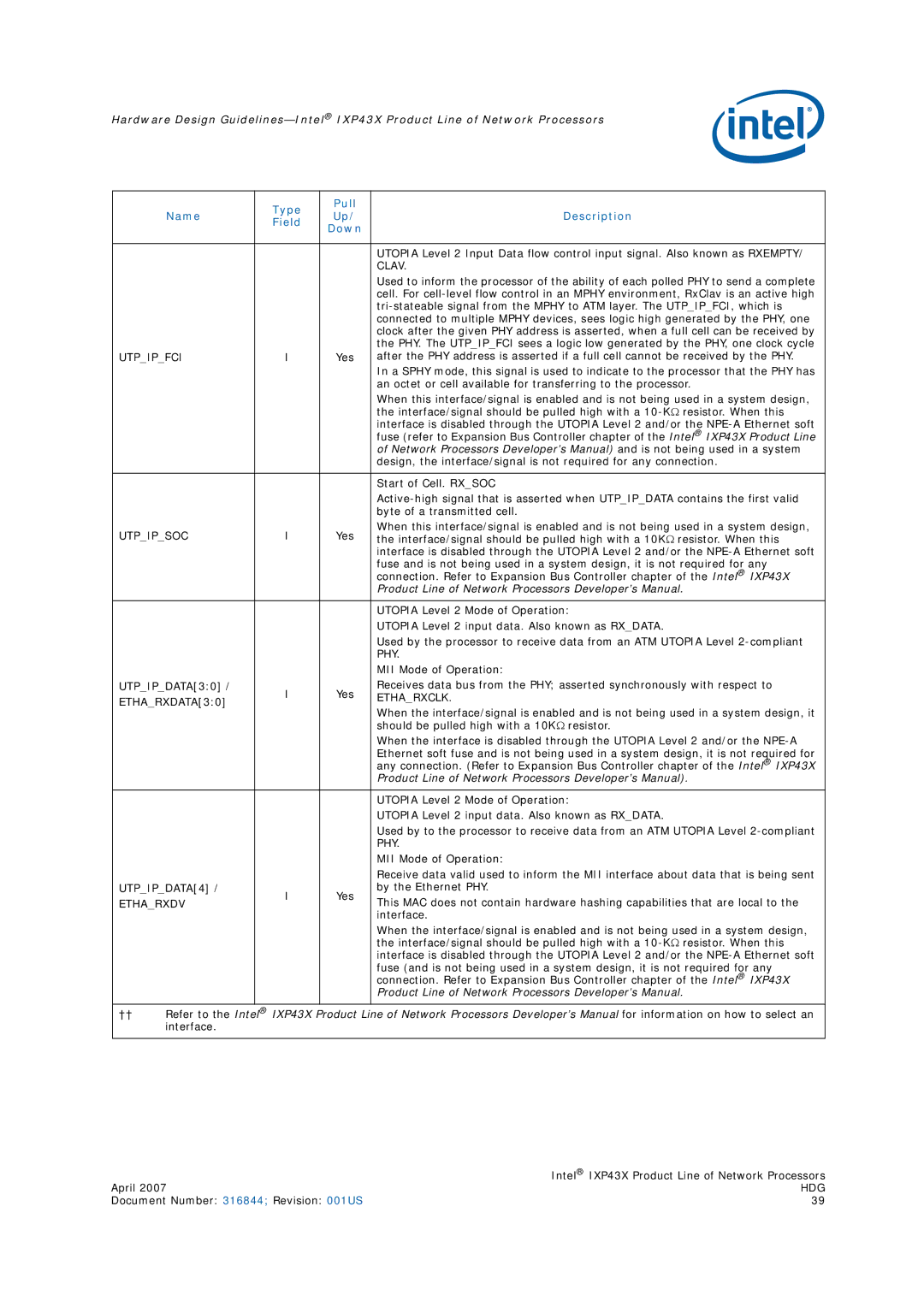

| UTOPIA Level 2 Input Data flow control input signal. Also known as RXEMPTY/ | |

|

|

|

| CLAV. | |

|

|

|

| Used to inform the processor of the ability of each polled PHY to send a complete | |

|

|

|

| cell. For | |

|

|

|

| ||

|

|

|

| connected to multiple MPHY devices, sees logic high generated by the PHY, one | |

|

|

|

| clock after the given PHY address is asserted, when a full cell can be received by | |

|

|

|

| the PHY. The UTP_IP_FCI sees a logic low generated by the PHY, one clock cycle | |

UTP_IP_FCI | I | Yes | after the PHY address is asserted if a full cell cannot be received by the PHY. | ||

|

|

|

| In a SPHY mode, this signal is used to indicate to the processor that the PHY has | |

|

|

|

| an octet or cell available for transferring to the processor. | |

|

|

|

| When this interface/signal is enabled and is not being used in a system design, | |

|

|

|

| the interface/signal should be pulled high with a | |

|

|

|

| interface is disabled through the UTOPIA Level 2 and/or the | |

|

|

|

| fuse (refer to Expansion Bus Controller chapter of the Intel® IXP43X Product Line | |

|

|

|

| of Network Processors Developer’s Manual) and is not being used in a system | |

|

|

|

| design, the interface/signal is not required for any connection. | |

|

|

|

|

| |

|

|

|

| Start of Cell. RX_SOC | |

|

|

|

| ||

|

|

|

| byte of a transmitted cell. | |

UTP_IP_SOC | I | Yes | When this interface/signal is enabled and is not being used in a system design, | ||

the interface/signal should be pulled high with a 10KΩ resistor. When this | |||||

|

|

|

| interface is disabled through the UTOPIA Level 2 and/or the | |

|

|

|

| fuse and is not being used in a system design, it is not required for any | |

|

|

|

| connection. Refer to Expansion Bus Controller chapter of the Intel® IXP43X | |

|

|

|

| Product Line of Network Processors Developer’s Manual. | |

|

|

|

|

| |

|

|

|

| UTOPIA Level 2 Mode of Operation: | |

|

|

|

| UTOPIA Level 2 input data. Also known as RX_DATA. | |

|

|

|

| Used by the processor to receive data from an ATM UTOPIA Level | |

|

|

|

| PHY. | |

|

|

|

| MII Mode of Operation: | |

UTP_IP_DATA[3:0] / | I | Yes | Receives data bus from the PHY; asserted synchronously with respect to | ||

ETHA_RXDATA[3:0] | ETHA_RXCLK. | ||||

|

| When the interface/signal is enabled and is not being used in a system design, it | |||

|

|

|

| ||

|

|

|

| should be pulled high with a 10KΩ resistor. | |

|

|

|

| When the interface is disabled through the UTOPIA Level 2 and/or the | |

|

|

|

| Ethernet soft fuse and is not being used in a system design, it is not required for | |

|

|

|

| any connection. (Refer to Expansion Bus Controller chapter of the Intel® IXP43X | |

|

|

|

| Product Line of Network Processors Developer’s Manual). | |

|

|

|

|

| |

|

|

|

| UTOPIA Level 2 Mode of Operation: | |

|

|

|

| UTOPIA Level 2 input data. Also known as RX_DATA. | |

|

|

|

| Used by to the processor to receive data from an ATM UTOPIA Level | |

|

|

|

| PHY. | |

|

|

|

| MII Mode of Operation: | |

|

|

|

| Receive data valid used to inform the MII interface about data that is being sent | |

UTP_IP_DATA[4] / | I | Yes | by the Ethernet PHY. | ||

ETHA_RXDV | This MAC does not contain hardware hashing capabilities that are local to the | ||||

|

| ||||

|

|

|

| interface. | |

|

|

|

| When the interface/signal is enabled and is not being used in a system design, | |

|

|

|

| the interface/signal should be pulled high with a | |

|

|

|

| interface is disabled through the UTOPIA Level 2 and/or the | |

|

|

|

| fuse (and is not being used in a system design, it is not required for any | |

|

|

|

| connection. Refer to Expansion Bus Controller chapter of the Intel® IXP43X | |

|

|

|

| Product Line of Network Processors Developer’s Manual. | |

|

|

|

|

| |

†† | Refer to the Intel® IXP43X Product Line of Network Processors Developer’s Manual for information on how to select an | ||||

| interface. |

|

|

| |

|

|

|

|

| |

| Intel® IXP43X Product Line of Network Processors |

April 2007 | HDG |

Document Number: 316844; Revision: 001US | 39 |