Intel® IXP43X Product Line of Network

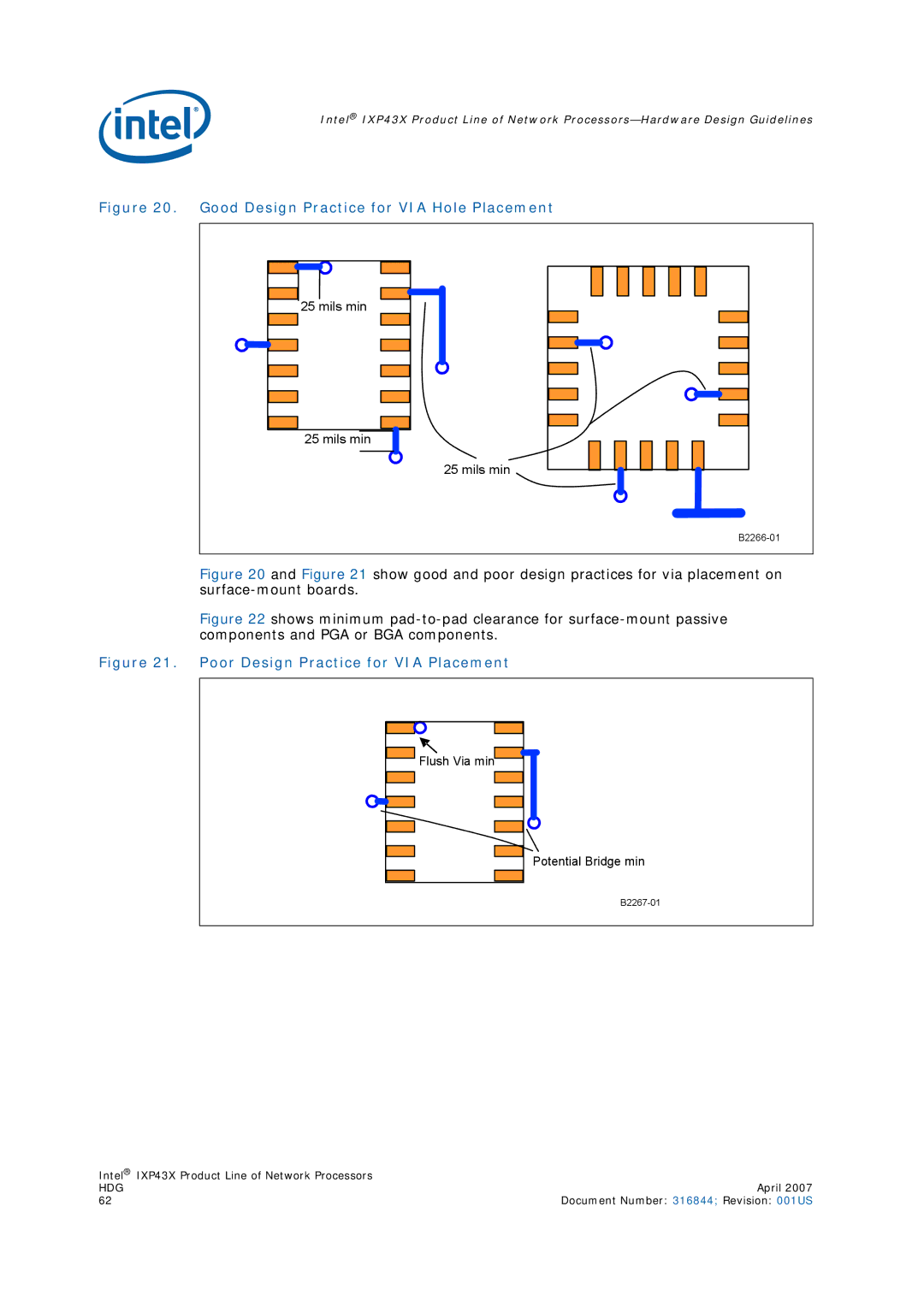

Figure 20. Good Design Practice for VIA Hole Placement

25 mils min

25 mils min

25 mils min

Figure 20 and Figure 21 show good and poor design practices for via placement on surface-mount boards.

Figure 22 shows minimum pad-to-pad clearance for surface-mount passive components and PGA or BGA components.

Figure 21. Poor Design Practice for VIA Placement

Flush Via min

Potential Bridge min

Intel® IXP43X Product Line of Network Processors |

|

HDG | April 2007 |

62 | Document Number: 316844; Revision: 001US |