Spectrum Signal Processing | Monaco Technical Reference |

| Global Shared Bus |

3 Global Shared Bus

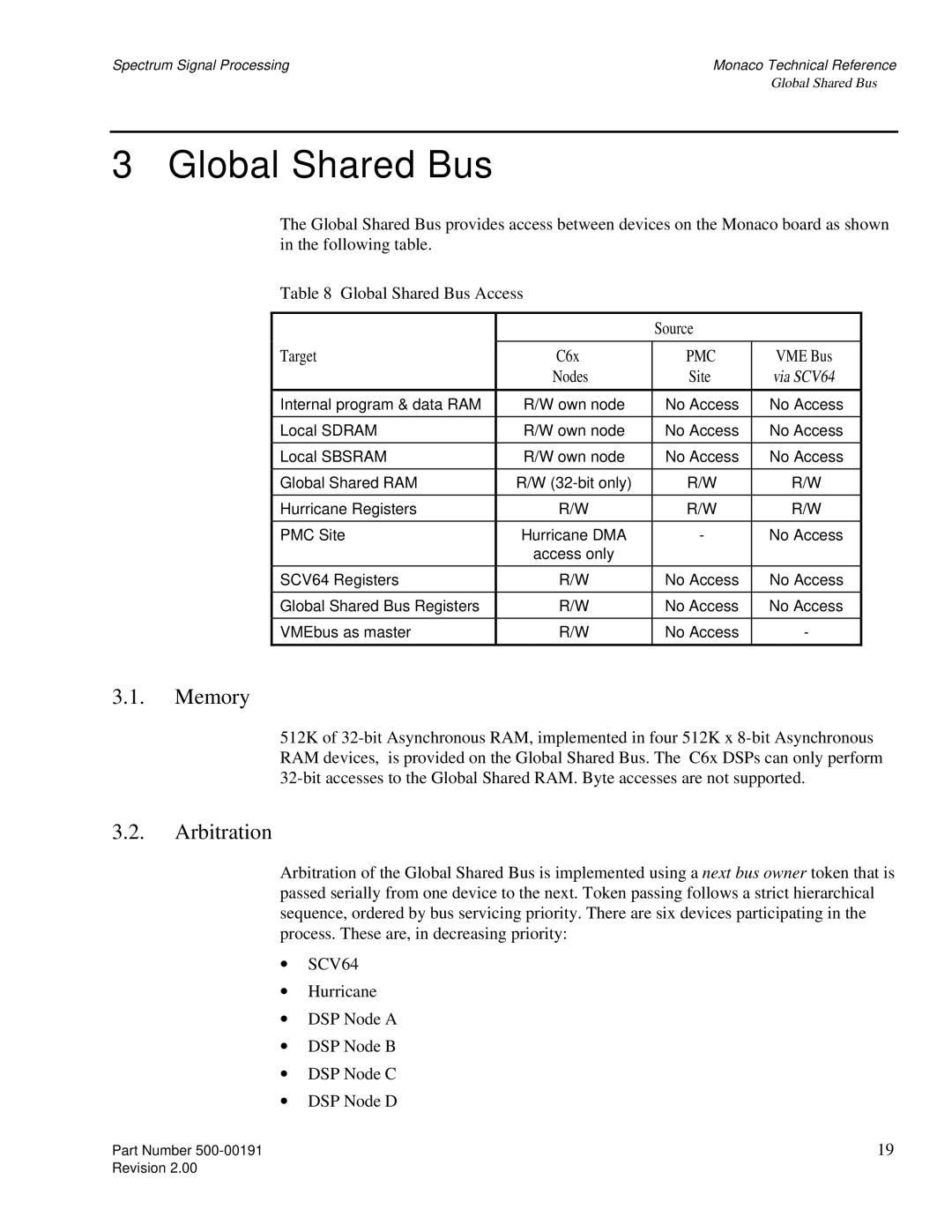

The Global Shared Bus provides access between devices on the Monaco board as shown in the following table.

Table 8 Global Shared Bus Access

|

| Source |

|

|

|

|

|

Target | ‘C6x | PMC | VME Bus |

| Nodes | Site | via SCV64 |

|

|

|

|

Internal program & data RAM | R/W own node | No Access | No Access |

|

|

|

|

Local SDRAM | R/W own node | No Access | No Access |

|

|

|

|

Local SBSRAM | R/W own node | No Access | No Access |

|

|

|

|

Global Shared RAM | R/W | R/W | R/W |

|

|

|

|

Hurricane Registers | R/W | R/W | R/W |

|

|

|

|

PMC Site | Hurricane DMA | - | No Access |

| access only |

|

|

|

|

|

|

SCV64 Registers | R/W | No Access | No Access |

|

|

|

|

Global Shared Bus Registers | R/W | No Access | No Access |

|

|

|

|

VMEbus as master | R/W | No Access | - |

|

|

|

|

3.1.Memory

512K of

3.2.Arbitration

Part Number

Arbitration of the Global Shared Bus is implemented using a next bus owner token that is passed serially from one device to the next. Token passing follows a strict hierarchical sequence, ordered by bus servicing priority. There are six devices participating in the process. These are, in decreasing priority:

∙SCV64

∙Hurricane

∙DSP Node A

∙DSP Node B

∙DSP Node C

∙DSP Node D

19