Monaco Technical Reference | Spectrum Signal Processing |

Processor Nodes |

|

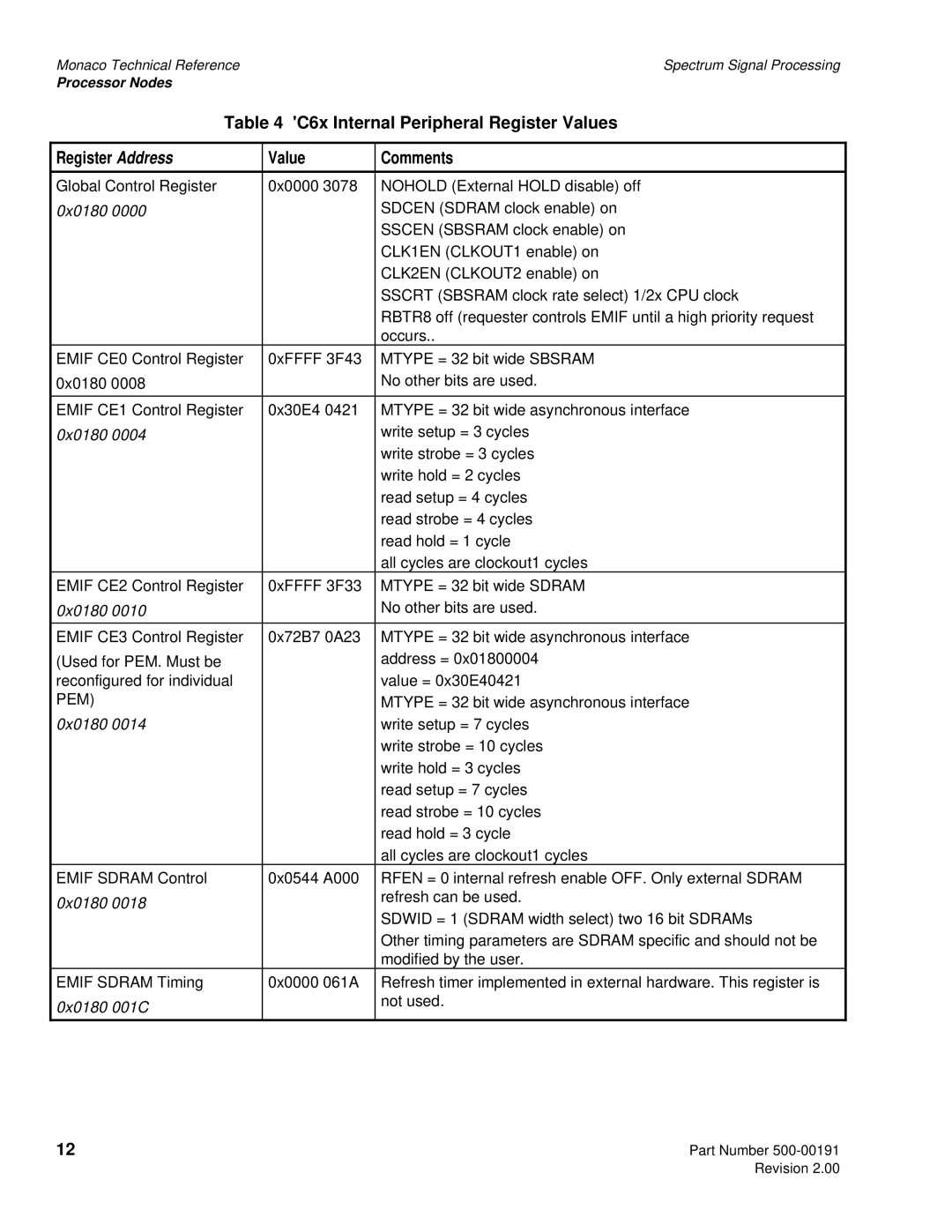

Table 4 'C6x Internal Peripheral Register Values

Register Address | Value | Comments |

|

|

|

Global Control Register | 0x0000 3078 | NOHOLD (External HOLD disable) off |

0x0180 0000 |

| SDCEN (SDRAM clock enable) on |

|

| SSCEN (SBSRAM clock enable) on |

|

| CLK1EN (CLKOUT1 enable) on |

|

| CLK2EN (CLKOUT2 enable) on |

|

| SSCRT (SBSRAM clock rate select) 1/2x CPU clock |

|

| RBTR8 off (requester controls EMIF until a high priority request |

|

| occurs.. |

EMIF CE0 Control Register | 0xFFFF 3F43 | MTYPE = 32 bit wide SBSRAM |

0x0180 0008 |

| No other bits are used. |

|

|

|

EMIF CE1 Control Register | 0x30E4 0421 | MTYPE = 32 bit wide asynchronous interface |

0x0180 0004 |

| write setup = 3 cycles |

|

| write strobe = 3 cycles |

|

| write hold = 2 cycles |

|

| read setup = 4 cycles |

|

| read strobe = 4 cycles |

|

| read hold = 1 cycle |

|

| all cycles are clockout1 cycles |

EMIF CE2 Control Register | 0xFFFF 3F33 | MTYPE = 32 bit wide SDRAM |

0x0180 0010 |

| No other bits are used. |

|

|

|

EMIF CE3 Control Register | 0x72B7 0A23 | MTYPE = 32 bit wide asynchronous interface |

(Used for PEM. Must be |

| address = 0x01800004 |

reconfigured for individual |

| value = 0x30E40421 |

PEM) |

| MTYPE = 32 bit wide asynchronous interface |

0x0180 0014 |

| write setup = 7 cycles |

|

| write strobe = 10 cycles |

|

| write hold = 3 cycles |

|

| read setup = 7 cycles |

|

| read strobe = 10 cycles |

|

| read hold = 3 cycle |

|

| all cycles are clockout1 cycles |

EMIF SDRAM Control | 0x0544 A000 | RFEN = 0 internal refresh enable OFF. Only external SDRAM |

0x0180 0018 |

| refresh can be used. |

| SDWID = 1 (SDRAM width select) two 16 bit SDRAMs | |

|

| |

|

| Other timing parameters are SDRAM specific and should not be |

|

| modified by the user. |

EMIF SDRAM Timing | 0x0000 061A | Refresh timer implemented in external hardware. This register is |

0x0180 001C |

| not used. |

|

| |

|

|

|

12 | Part Number |

| Revision 2.00 |