Spectrum Signal Processing | Monaco Technical Reference |

| Registers |

9 Registers

This section provides a reference to the registers that are unique to the Monaco board. Information for the registers within the SCV64 bus interface chip, the ACT8990 Test Bus Controller (TBC), and the Hurricane PCI interface chip can be found in their respective data sheets.

Most of the registers described in this section are accessed from the processor nodes. Of these, most are shared among nodes A, B, C, and D. A few, though, are unique to each node. The registers that are not accessible from the processor nodes are part of the VME A24 Host Port Interfaces and to the TBC.

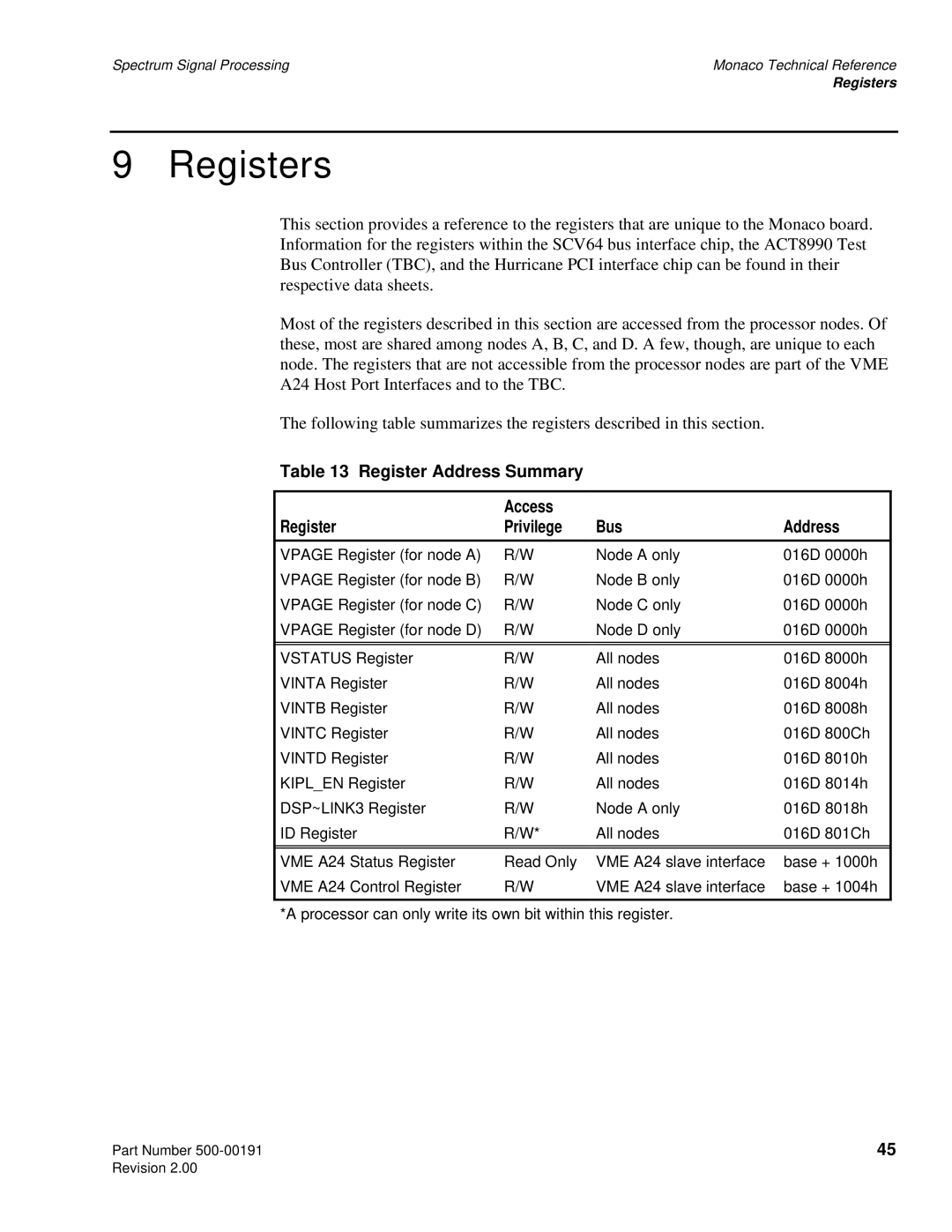

The following table summarizes the registers described in this section.

Table 13 Register Address Summary

| Access |

|

|

|

Register | Privilege | Bus | Address | |

|

|

|

|

|

VPAGE Register (for node A) | R/W | Node A only | 016D | 0000h |

VPAGE Register (for node B) | R/W | Node B only | 016D | 0000h |

VPAGE Register (for node C) | R/W | Node C only | 016D | 0000h |

VPAGE Register (for node D) | R/W | Node D only | 016D | 0000h |

|

|

|

|

|

|

|

|

|

|

VSTATUS Register | R/W | All nodes | 016D | 8000h |

VINTA Register | R/W | All nodes | 016D | 8004h |

VINTB Register | R/W | All nodes | 016D | 8008h |

VINTC Register | R/W | All nodes | 016D | 800Ch |

VINTD Register | R/W | All nodes | 016D | 8010h |

KIPL_EN Register | R/W | All nodes | 016D 8014h | |

DSP~LINK3 Register | R/W | Node A only | 016D 8018h | |

ID Register | R/W* | All nodes | 016D | 801Ch |

|

|

|

| |

|

|

|

| |

VME A24 Status Register | Read Only | VME A24 slave interface | base + 1000h | |

VME A24 Control Register | R/W | VME A24 slave interface | base + 1004h | |

|

|

|

|

|

*A processor can only write its own bit within this register.

Part Number | 45 |

Revision 2.00 |

|