Monaco Technical Reference | Spectrum Signal Processing |

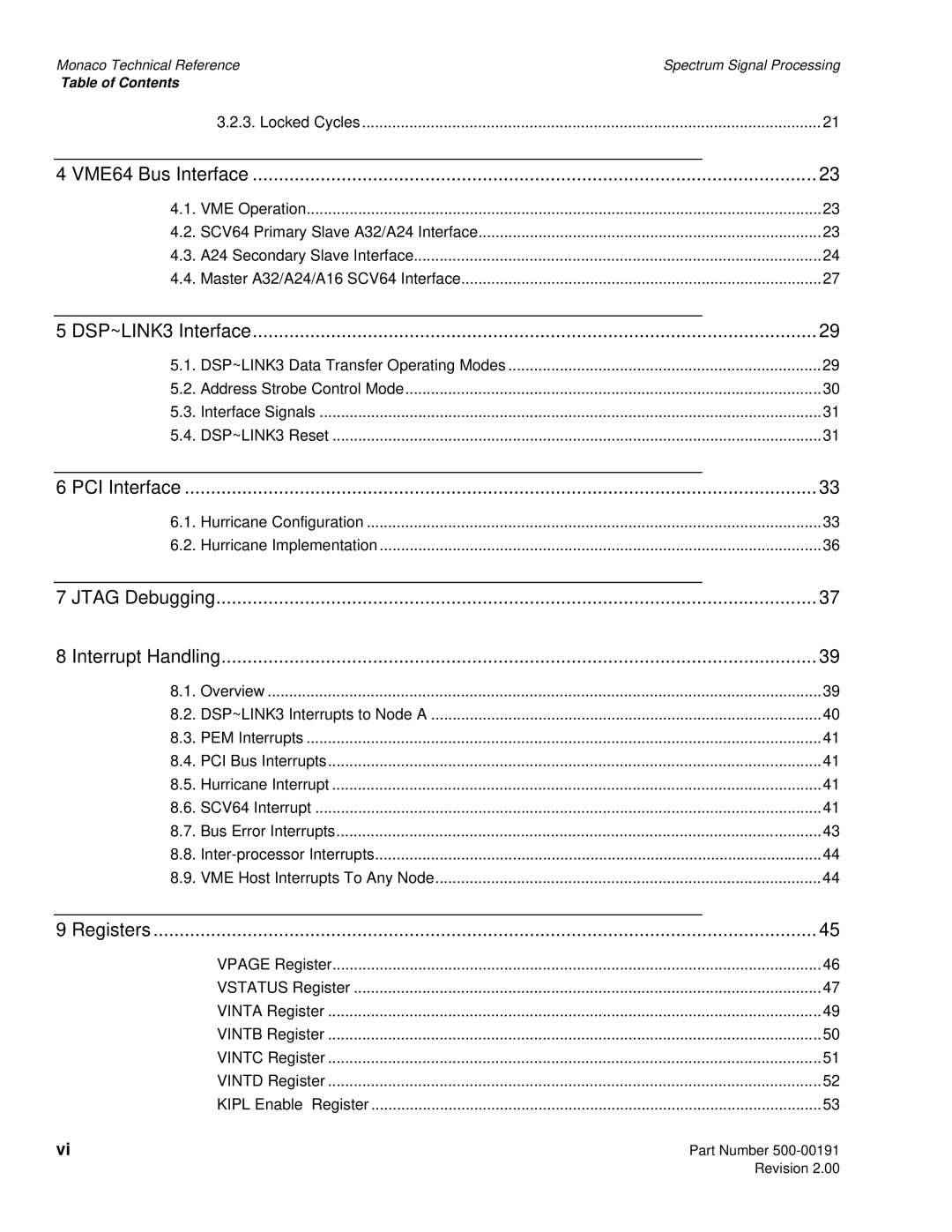

Table of Contents |

|

3.2.3. Locked Cycles | 21 |

4 VME64 Bus Interface | 23 |

4.1. VME Operation | 23 |

4.2. SCV64 Primary Slave A32/A24 Interface | 23 |

4.3. A24 Secondary Slave Interface | 24 |

4.4. Master A32/A24/A16 SCV64 Interface | 27 |

5 DSP~LINK3 Interface | 29 |

5.1. DSP~LINK3 Data Transfer Operating Modes | 29 |

5.2. Address Strobe Control Mode | 30 |

5.3. Interface Signals | 31 |

5.4. DSP~LINK3 Reset | 31 |

6 PCI Interface | 33 |

6.1. Hurricane Configuration | 33 |

6.2. Hurricane Implementation | 36 |

7 JTAG Debugging | 37 |

8 Interrupt Handling | 39 |

8.1. Overview | 39 |

8.2. DSP~LINK3 Interrupts to Node A | 40 |

8.3. PEM Interrupts | 41 |

8.4. PCI Bus Interrupts | 41 |

8.5. Hurricane Interrupt | 41 |

8.6. SCV64 Interrupt | 41 |

8.7. Bus Error Interrupts | 43 |

8.8. | 44 |

8.9. VME Host Interrupts To Any Node | 44 |

9 Registers | 45 |

VPAGE Register | 46 |

VSTATUS Register | 47 |

VINTA Register | 49 |

VINTB Register | 50 |

VINTC Register | 51 |

VINTD Register | 52 |

KIPL Enable Register | 53 |

vi | Part Number |

| Revision 2.00 |