Monaco Technical Reference | Spectrum Signal Processing |

Registers

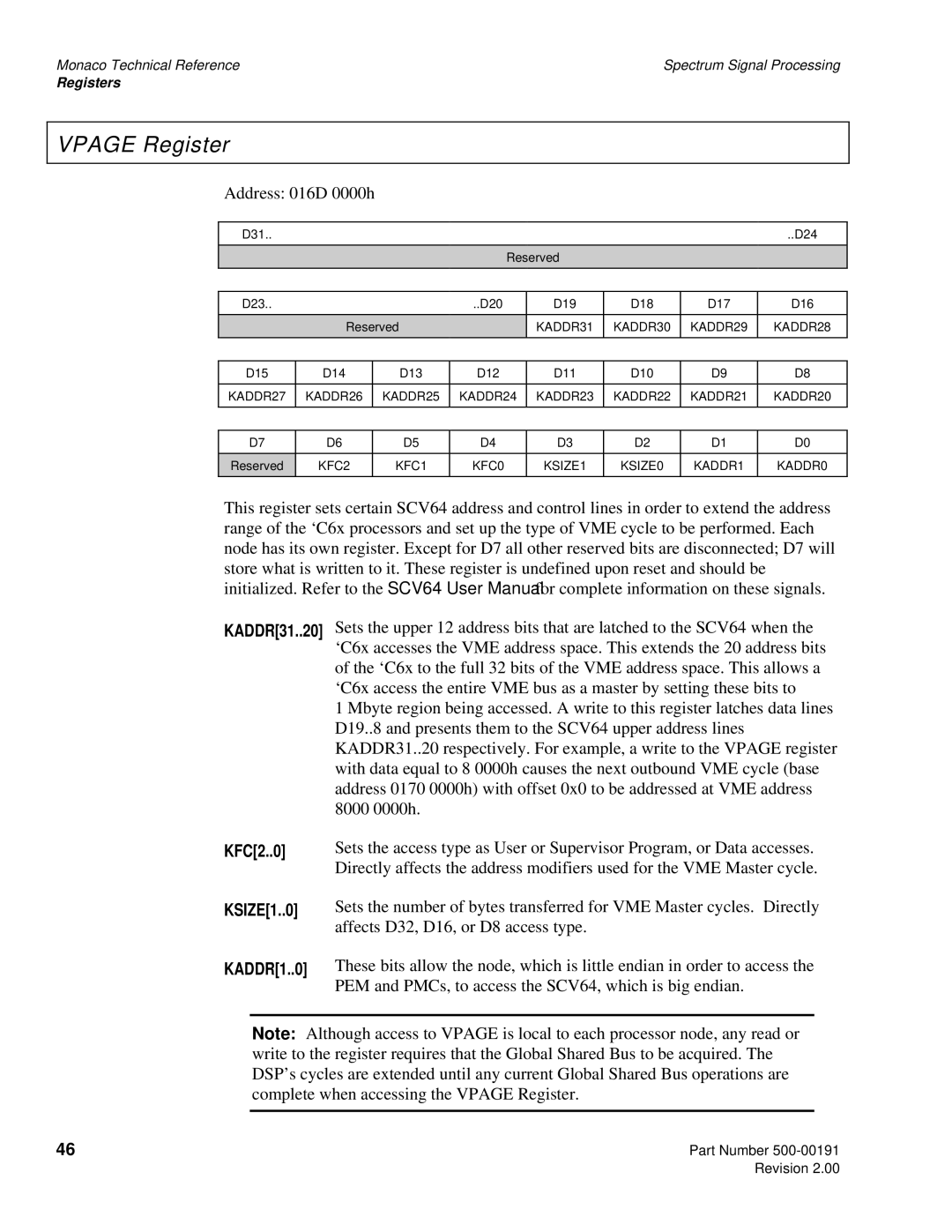

VPAGE Register

Address: 016D 0000h

D31.. |

|

|

|

|

|

| ..D24 |

|

|

|

|

|

|

|

|

|

|

| Reserved |

|

|

| |

|

|

|

|

|

|

|

|

D23.. |

|

| ..D20 | D19 | D18 | D17 | D16 |

|

|

|

|

|

|

|

|

| Reserved |

| KADDR31 | KADDR30 | KADDR29 | KADDR28 | |

|

|

|

|

|

|

|

|

D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 |

|

|

|

|

|

|

|

|

KADDR27 | KADDR26 | KADDR25 | KADDR24 | KADDR23 | KADDR22 | KADDR21 | KADDR20 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|

|

|

|

|

|

|

|

Reserved | KFC2 | KFC1 | KFC0 | KSIZE1 | KSIZE0 | KADDR1 | KADDR0 |

|

|

|

|

|

|

|

|

This register sets certain SCV64 address and control lines in order to extend the address range of the ‘C6x processors and set up the type of VME cycle to be performed. Each node has its own register. Except for D7 all other reserved bits are disconnected; D7 will store what is written to it. These register is undefined upon reset and should be initialized. Refer to the SCV64 User Manual for complete information on these signals.

KADDR[31..20] Sets the upper 12 address bits that are latched to the SCV64 when the ‘C6x accesses the VME address space. This extends the 20 address bits

of the ‘C6x to the full 32 bits of the VME address space. This allows a ‘C6x access the entire VME bus as a master by setting these bits to

1 Mbyte region being accessed. A write to this register latches data lines D19..8 and presents them to the SCV64 upper address lines KADDR31..20 respectively. For example, a write to the VPAGE register with data equal to 8 0000h causes the next outbound VME cycle (base address 0170 0000h) with offset 0x0 to be addressed at VME address 8000 0000h.

KFC[2..0]

KSIZE[1..0]

KADDR[1..0]

Sets the access type as User or Supervisor Program, or Data accesses. Directly affects the address modifiers used for the VME Master cycle.

Sets the number of bytes transferred for VME Master cycles. Directly affects D32, D16, or D8 access type.

These bits allow the node, which is little endian in order to access the PEM and PMCs, to access the SCV64, which is big endian.

Note: Although access to VPAGE is local to each processor node, any read or write to the register requires that the Global Shared Bus to be acquired. The DSP’s cycles are extended until any current Global Shared Bus operations are complete when accessing the VPAGE Register.

46 | Part Number |

| Revision 2.00 |