Monaco Technical Reference | Spectrum Signal Processing |

Interrupt Handling

The /KIPL[2..0] status bits, D[2..0], in the VSTATUS Register indicate the priority level of the SCV64 interrupt. These bits reflect the state of the /KIPL lines from the SCV64. If all three

If the interrupt was due to an SCV64 interrupt, it is serviced by performing an IACK cycle to the SCV64. An IACK cycle is a special type of VME read cycle to a specific location in the IACK cycle space (base address 016F 0000h).

For an IACK read cycle, bits D[0..7] of the VPAGE Register must be initialized in the following way:

∙KADDR0 (bit D0) is set to “0”

∙The value of the /KIPL0 bit in the VSTATUS Register is inverted and placed in the KADDR1 bit (bit D1)

∙KSIZE0 (bit D2) is set to “1”

∙KSIZE1 (bit D3) is set to “0”

∙All three KFC bits (bits D[6..4]) are set to “1”

The /KIPL[2..1] status bits, D[2..1], in the VSTATUS Register determine the offset of the address to read within the IACK cycle space.

∙/KIPL2 is inverted to determine IACK address bit A3

∙/KIPL1 is inverted to determine IACK address bit A2

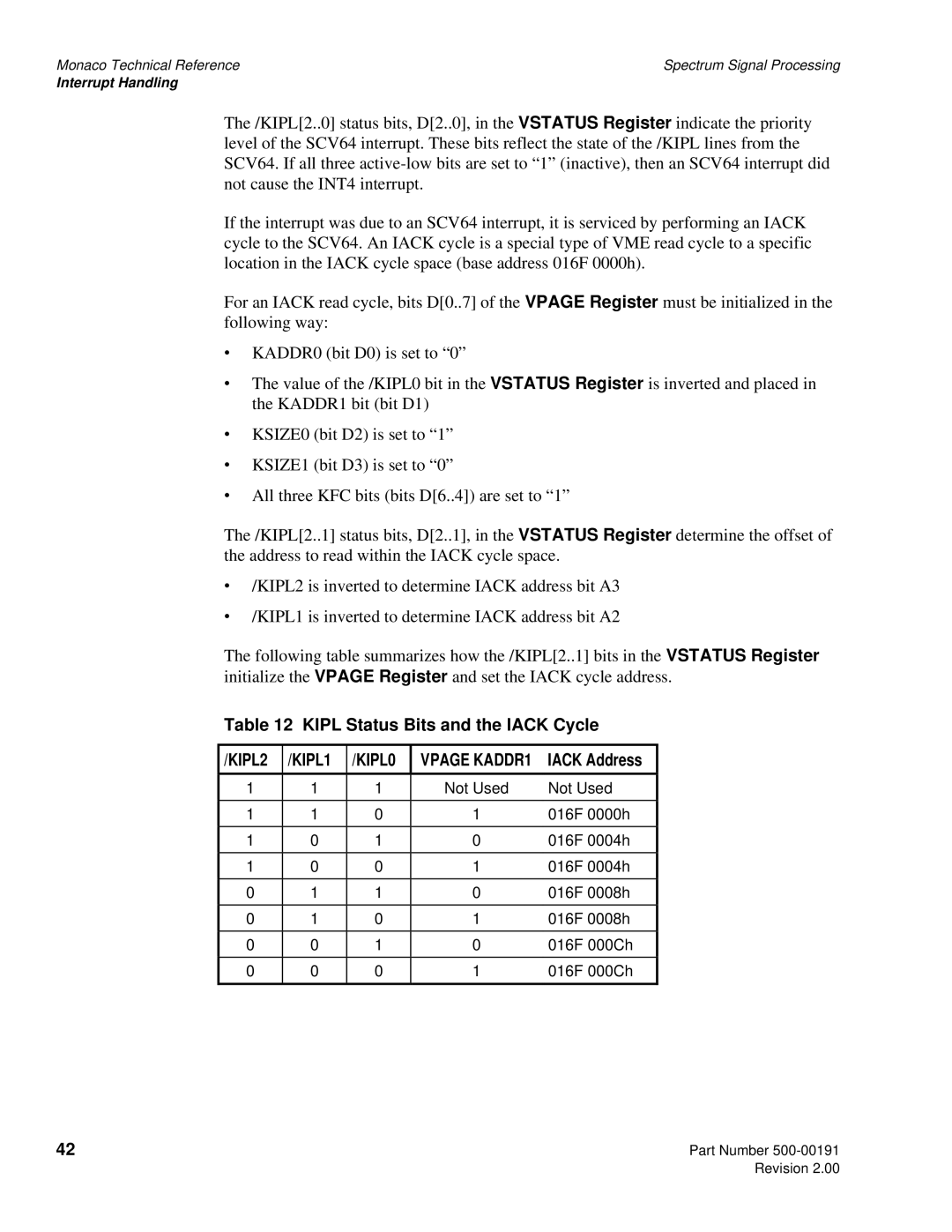

The following table summarizes how the /KIPL[2..1] bits in the VSTATUS Register initialize the VPAGE Register and set the IACK cycle address.

Table 12 KIPL Status Bits and the IACK Cycle

/KIPL2 | /KIPL1 | /KIPL0 | VPAGE KADDR1 | IACK Address | |

|

|

|

|

| |

1 | 1 | 1 | Not Used | Not Used | |

|

|

|

|

|

|

1 | 1 | 0 | 1 | 016F | 0000h |

|

|

|

|

|

|

1 | 0 | 1 | 0 | 016F | 0004h |

|

|

|

|

|

|

1 | 0 | 0 | 1 | 016F | 0004h |

|

|

|

|

|

|

0 | 1 | 1 | 0 | 016F | 0008h |

|

|

|

|

|

|

0 | 1 | 0 | 1 | 016F | 0008h |

|

|

|

|

|

|

0 | 0 | 1 | 0 | 016F | 000Ch |

|

|

|

|

|

|

0 | 0 | 0 | 1 | 016F | 000Ch |

|

|

|

|

|

|

42 | Part Number |

| Revision 2.00 |