Monaco Technical Reference | Spectrum Signal Processing |

Registers

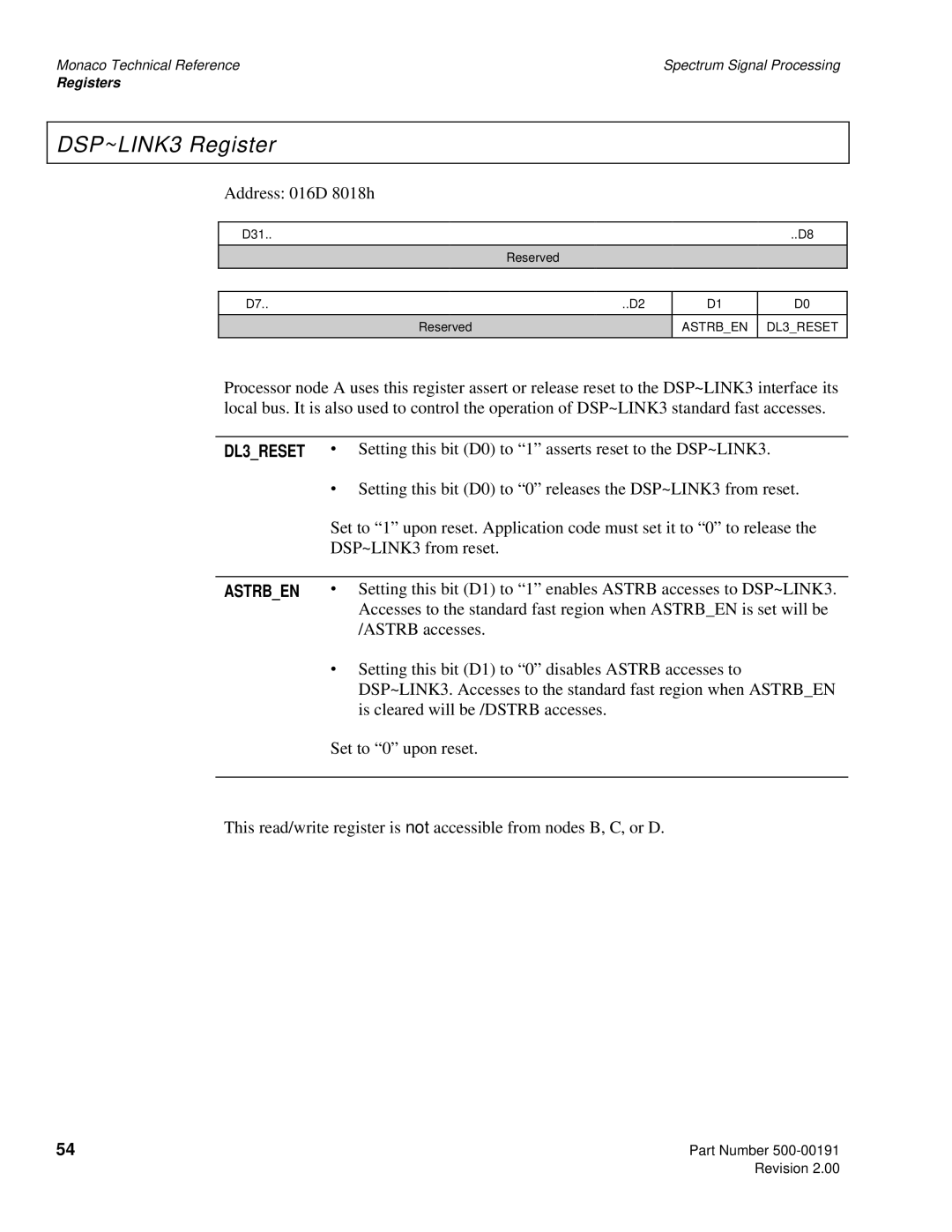

DSP~LINK3 Register

Address: 016D 8018h

D31.. |

|

| ..D8 |

|

|

|

|

| Reserved |

|

|

|

|

|

|

D7.. | ..D2 | D1 | D0 |

|

|

|

|

Reserved |

| ASTRB_EN | DL3_RESET |

|

|

|

|

Processor node A uses this register assert or release reset to the DSP~LINK3 interface its local bus. It is also used to control the operation of DSP~LINK3 standard fast accesses.

DL3_RESET | ∙ Setting this bit (D0) to “1” asserts reset to the DSP~LINK3. |

| ∙ Setting this bit (D0) to “0” releases the DSP~LINK3 from reset. |

| Set to “1” upon reset. Application code must set it to “0” to release the |

| DSP~LINK3 from reset. |

|

|

ASTRB_EN | ∙ Setting this bit (D1) to “1” enables ASTRB accesses to DSP~LINK3. |

| Accesses to the standard fast region when ASTRB_EN is set will be |

| /ASTRB accesses. |

| ∙ Setting this bit (D1) to “0” disables ASTRB accesses to |

| DSP~LINK3. Accesses to the standard fast region when ASTRB_EN |

| is cleared will be /DSTRB accesses. |

| Set to “0” upon reset. |

|

|

This read/write register is not accessible from nodes B, C, or D.

54 | Part Number |

| Revision 2.00 |