Spectrum Signal Processing | Monaco Technical Reference |

| PCI Interface |

6 PCI Interface

The Hurricane chip provides the interface between the Global Shared SRAM on the Global Shared Bus and the PMC site which supports a 32 bit, 33 MHz PCI bus. Although the DSPs cannot directly master the PCI bus, the Hurricane’s DMA controller provides flexible data transfer between the Global Shared Bus SRAM and the PMC.

Embedded PCI buses require Hurricane PCI configuration cycle generation.

PMC modules can directly master the Global Shared SRAM.

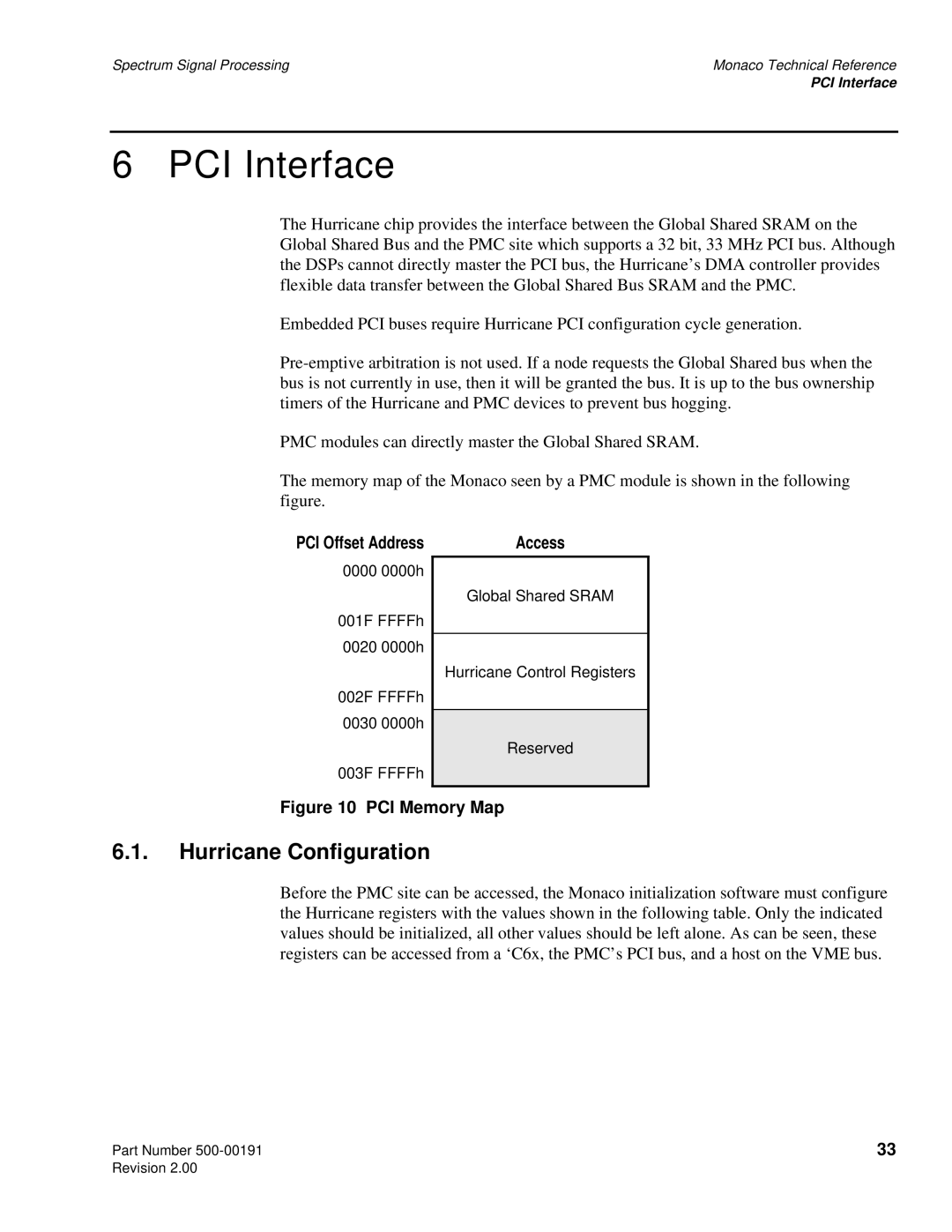

The memory map of the Monaco seen by a PMC module is shown in the following figure.

PCI Offset Address | Access |

0000 0000h

001F FFFFh

0020 0000h

002F FFFFh

0030 0000h

003F FFFFh

Global Shared SRAM

Hurricane Control Registers

Reserved

Figure 10 PCI Memory Map

6.1.Hurricane Configuration

Before the PMC site can be accessed, the Monaco initialization software must configure the Hurricane registers with the values shown in the following table. Only the indicated values should be initialized, all other values should be left alone. As can be seen, these registers can be accessed from a ‘C6x, the PMC’s PCI bus, and a host on the VME bus.

Part Number | 33 |

Revision 2.00 |

|