Spectrum Signal Processing | Monaco Technical Reference |

| Registers |

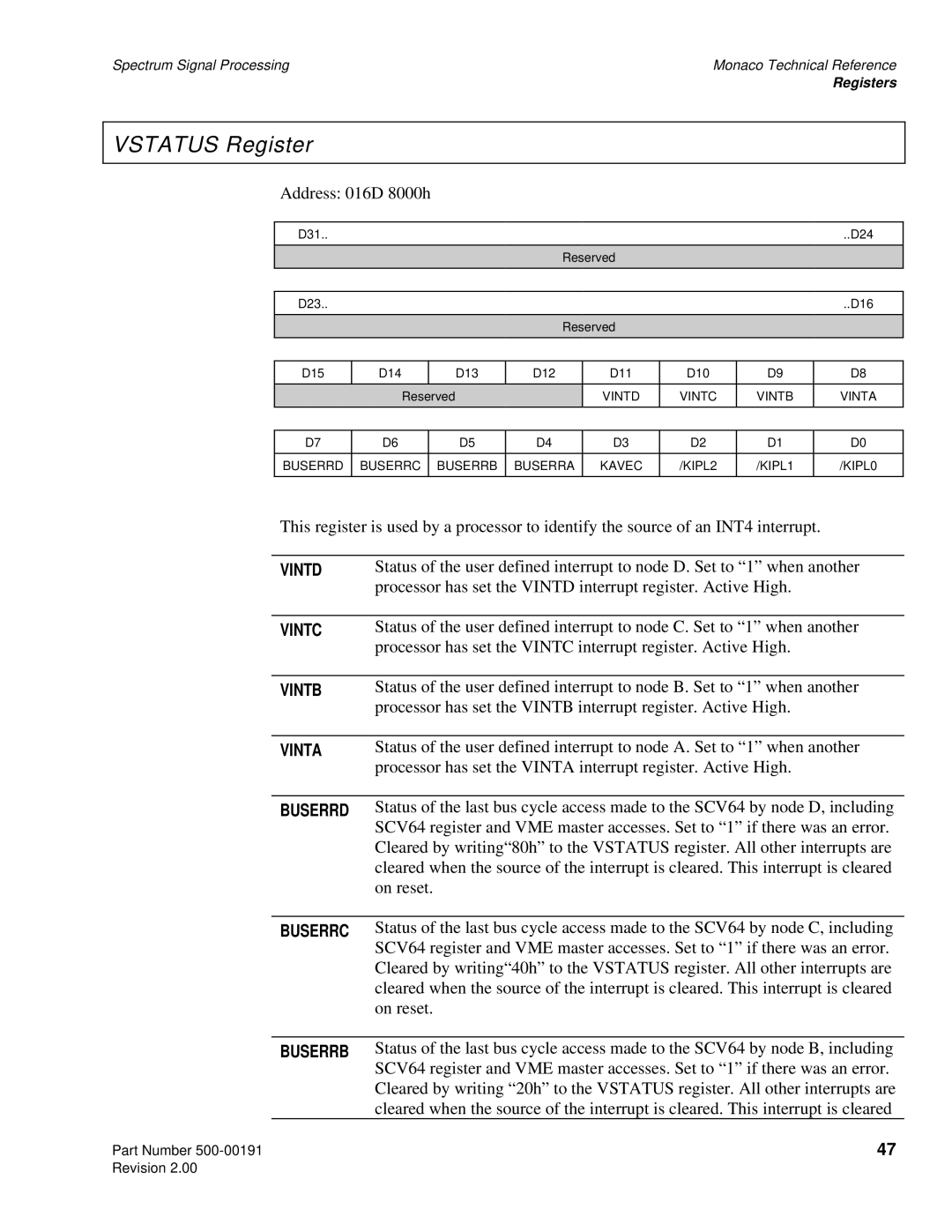

VSTATUS Register

Address: 016D 8000h

D31.. |

|

|

|

|

|

| ..D24 |

|

|

|

|

|

|

|

|

|

|

| Reserved |

|

|

| |

|

|

|

|

|

|

|

|

D23.. |

|

|

|

|

|

| ..D16 |

|

|

|

|

|

|

|

|

|

|

| Reserved |

|

|

| |

|

|

|

|

|

|

|

|

D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 |

|

|

|

|

|

|

|

|

| Reserved |

| VINTD | VINTC | VINTB | VINTA | |

|

|

|

|

|

|

|

|

D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|

|

|

|

|

|

|

|

BUSERRD | BUSERRC | BUSERRB | BUSERRA | KAVEC | /KIPL2 | /KIPL1 | /KIPL0 |

|

|

|

|

|

|

|

|

This register is used by a processor to identify the source of an INT4 interrupt.

| VINTD | Status of the user defined interrupt to node D. Set to “1” when another |

|

| processor has set the VINTD interrupt register. Active High. |

|

|

|

| VINTC | Status of the user defined interrupt to node C. Set to “1” when another |

|

| processor has set the VINTC interrupt register. Active High. |

|

|

|

| VINTB | Status of the user defined interrupt to node B. Set to “1” when another |

|

| processor has set the VINTB interrupt register. Active High. |

|

|

|

| VINTA | Status of the user defined interrupt to node A. Set to “1” when another |

|

| processor has set the VINTA interrupt register. Active High. |

|

|

|

| BUSERRD | Status of the last bus cycle access made to the SCV64 by node D, including |

|

| SCV64 register and VME master accesses. Set to “1” if there was an error. |

|

| Cleared by writing“80h” to the VSTATUS register. All other interrupts are |

|

| cleared when the source of the interrupt is cleared. This interrupt is cleared |

|

| on reset. |

|

|

|

| BUSERRC | Status of the last bus cycle access made to the SCV64 by node C, including |

|

| SCV64 register and VME master accesses. Set to “1” if there was an error. |

|

| Cleared by writing“40h” to the VSTATUS register. All other interrupts are |

|

| cleared when the source of the interrupt is cleared. This interrupt is cleared |

|

| on reset. |

|

|

|

| BUSERRB | Status of the last bus cycle access made to the SCV64 by node B, including |

|

| SCV64 register and VME master accesses. Set to “1” if there was an error. |

|

| Cleared by writing “20h” to the VSTATUS register. All other interrupts are |

|

| cleared when the source of the interrupt is cleared. This interrupt is cleared |

Part Number | 47 | |

Revision 2.00 |

| |